# Modelling and Verification of Real-Time Systems Using Timed Automata: Theory and Practice

Paul Pettersson

A Dissertation submitted for the Degree of Doctor of Philosophy Department of Computer Systems Uppsala University

February 1999

ISSN 0283-0574

Dissertation for the Degree of Doctor of Philosophy in Computer Systems presented at Uppsala University in 1999.

## ABSTRACT

Pettersson, P. 1999: Modelling and Verification of Real-Time Systems Using Timed Automata: Theory and Practice. DoCS 99/101. 206 pp. Uppsala. ISSN 0283-0574.

During the last decade, model-checking techniques for the verification of timed system have been developed based on the theory of timed automata. The practical limitation in applying these techniques to industrial-size systems is the huge amount of time and memory needed to explore and store the state-space of the system model.

In this thesis, we improve the current status of model-checking techniques for timed systems by developing symbolic, on-the-fly and compositional verification techniques for timed automata. A common characteristics of the model-checking techniques presented is that they use efficient constraint-solving techniques to symbolically represent and manipulate the state-space. To avoid construction of the full state-space of the system model two techniques are used: on-the-fly generation of the state-space and a compositional model-checking technique. The memory-usage is further reduced by developing a minimal and canonical data structure for the class of constraints used in the model-checking algorithm, which reduces the size of each individual state. Two other techniques to reduce the total number of states explored and stored during verification are also presented.

The developed techniques have been implemented in the verification tool UPPAAL. To demonstrate the potential applications of our model-checking techniques, we present three industrial-size case studies where the UPPAAL tool is applied.

Paul Pettersson, Department of Computer Systems, Uppsala University, Box 325, S-751 05 Uppsala, Sweden, Email: paupet@docs.uu.se

© Paul Pettersson 1999

ISSN 0283-0574

Printed in Sweden by Nina Tryckeri HB, Uppsala 1999.

Distributor: Department of Computer Systems, Uppsala University, Box 325, S-751 05 Uppsala, Sweden.

Till Sara, Egil och Frej

# Acknowledgements

This thesis would not have been possible without the advice and support of my supervisor and friend Wang Yi. He has, during my five years as graduate student, guided me with enthusiasm and great humour, and supported me to grow as a researcher. I am very grateful for his thorough reviewing of this thesis and our collaboration that has resulted in a number of publications, of which several are included in this thesis.

I am also grateful to my other colleagues in the "UPPAAL group" at the Department of Computers System (DoCS) at Uppsala University, i.e. Tobias Amnell, Johan Bengtsson, Alexandre David, Fredrik Larsson and Justin Pearson for the stimulating environment. In particular, I would like to thank Johan Bengtsson and Fredrik Larsson for their excellent work in implementing the UPPAAL tool over the years and many fruitful discussions.

I would like to thank Bengt Jonsson and Kim G. Larsen for their continuous support over the years. I have benefitted a lot from their insights in theoretical computer science. In particular, I thank Kim for co-authoring several papers included in this thesis, and other publications not included. I thank him also for giving me the opportunity to visit the Department of Computer Science at Aalborg University in Denmark during ten weeks in 1995.

I acknowledge my other co-authors, i.e. Mats Daniels. W. O. David Griffioen, Kåre J. Kristoffersen, Francois Laroussinie, Magnus Lindahl and Henrik Lönn. Thank you for your cooperativeness and for the fun we had in writing the papers and presenting them at conferences.

Of all my friends and colleagues at DoCS, I like to thank in particular Hans Hansson for his support and leadership in the ASTEC-RT project, the secretaries Helena Pettersson and Inga-Lisa Ericsson, and the system administrators Per Lindgren and Anders Andersson for all the help I received over the years.

I would like to thank Tiziana Margaria for her constructive comments on an early version of this thesis.

To my fiance Sara Magnusson I can only say thank you. She has sacrificed a lot for this thesis, especially during the last months; she has my deepest gratitude and love. Finally, I thank my two sons Egil and Frej who are my best sources of inspiration and motivation. I am sorry that we have not been able to play much lately, I will probably have more time now...

This work has been partially supported by the Swedish Board for Technical Development (NUTEK), the Swedish Technical Research Council (TFR) and the competence center for Advanced Software TEChnology (ASTEC) at Uppsala University.

This thesis is based on seven revised versions of papers published in 1994 to 1998. In the introduction the papers will be referred to as papers A through G.

- [A] Wang Yi, Paul Pettersson, and Mats Daniels. Automatic Verification of Real-Time Communicating Systems By Constraint-Solving. In Dieter Hogrefe and Stefan Leue, editors, Proc. of the 7th Int. Conf. on Formal Description Techniques, pages 223–238. North-Holland 1994.

- [B] Kim G. Larsen, Paul Pettersson, and Wang Yi. Compositional and Symbolic Model-Checking of Real-Time Systems. In Proc. of the 16th Real-Time Systems Symposium, pages 76-87. IEEE Computer Society Press 1995.

- [C] Kim G. Larsen, Paul Pettersson, and Wang Yi. Diagnostic Model-Checking for Real-Time Systems. In Rajeev Alur, Thomas A. Henzinger and Eduardo D. Sontag, editors, Proc. of Workshop on Verification and Control of Hybrid Systems III, number 1066 in Lecture Notes in Computer Science, pages 575–586. Springer-Verlag 1995.

- [D] Fredrik Larsson, Kim G. Larsen, Paul Pettersson, and Wang Yi. Efficient Verification of Real-Time Systems: Compact Data Structures and State-Space Reduction. In Proc. of the 18th Real-Time Systems Symposium, pages 14-24. IEEE Computer Society Press 1997.

- [E] Johan Bengtsson, W. O. David Griffioen, Kåre J. Kristoffersen, Kim G. Larsen, Fredrik Larsson, Paul Pettersson, and Wang Yi. Verification of an Audio Protocol with Bus Collision Using UPPAAL. In Rajeev Alur and Thomas A. Henzinger, editors, *Proc. of 9th Int. Conf. on Computer Aided Verification*, number 1102 in Lecture Notes in Computer Science, pages 244–256. Springer–Verlag 1996.

- [F] Henrik Lönn and Paul Pettersson. Formal Verification of a TDMA Protocol Startup Mechanism. In Proc. of the Pacific Rim International Symposium on Fault-Tolerant Systems, pages 235–242. IEEE Computer Society Press 1997.

- [G] Magnus Lindahl, Paul Pettersson, and Wang Yi. Formal Design and Analysis of a Gear-Box Controller. In Bernhard Steffen, editor, Proc. of the 4th Workshop on Tools and Algorithms for the Construction and Analysis of Systems, number 1384 in Lecture Notes in Computer Science, pages 281–297. Springer-Verlag 1998. Invited for publication in International Journal on Software Tools for Technology Transfer.

### **Comments on My Participation**

All the papers included in this thesis are revised by me and Wang Yi.

- **Paper A:** I participated in discussions and made the prototype implementation. All the proofs are by me and Wang Yi.

- **Paper B:** I participated in discussions and wrote the section on experiments included in the conference version of the paper.

- **Paper C:** I participated in discussions and wrote a large part of the paper. The case study is due to me.

- **Paper D:** I participated in discussions and made the experiments. I wrote part of the paper.

- **Paper E:** I participated in discussions. W. O. David Griffioen and I wrote sections 4 to 6.

- Paper F: Henrik Lönn and I modelled the protocol. I wrote part of the paper.

- **Paper G:** Magnus Lindahl and I modelled and synthesised the model of the gearbox controller and wrote sections 4 to 6.

# Contents

| In  | troduction                            | 1              |

|-----|---------------------------------------|----------------|

| 1   | Background                            | 3              |

|     | 1.1 Real-Time Systems                 | 4              |

|     | 1.2 Timed Automata                    | 5              |

|     | 1.3 Automatic Verification            | $\overline{7}$ |

| 2   | Summary of Results                    | 10             |

|     | 2.1 Symbolic Verification Algorithms  | 10             |

|     | 2.2 Memory Usage Reduction            | 11             |

|     | 2.3 Verification Tool Development     | 12             |

|     | 2.4 Case Studies                      | 14             |

| 3   | Related Work                          | 16             |

|     | 3.1 Verification of Real-Time Systems | 16             |

|     | 3.2 Tool Development                  | 17             |

|     | 3.3 Case Studies                      | 18             |

| 4   | Conclusion and Future Work            | 19             |

| 5   | Outline of the Thesis                 | 21             |

| Ref | erences                               | 22             |

# II Algorithms and Data Structures

| Paper 4 | A: Automatic Verification of Real-Time Communicating Systems |    |

|---------|--------------------------------------------------------------|----|

| by (    | Constraint-Solving 3                                         | 3  |

| 1       | Introduction                                                 | 35 |

| 2       | An Algebra of Processes with Clocks                          | 37 |

|         | 2.1 Syntax                                                   | 37 |

|         |                                                              | 88 |

| 3       | Symbolic Semantics of Processes                              | 10 |

|         | 3.1 Operations on Clock Constraints                          | 11 |

|         | 3.2 Symbolic Transition Rules                                | 11 |

| 4       | Finite Symbolic Semantics of Processes                       | 14 |

|         | 4.1 Normalisation of Clock Constraints                       | 15 |

|         | 4.2 Normalised Symbolic Transition Rules                     | 16 |

| 5       | Checking Safety Properties of Processes                      | 19 |

|         | 5.1 Reachability Analysis                                    | 19 |

|         | 5.2 An Algorithm for Reachability Analysis                   | 19 |

| 6       | Examples                                                     | 52 |

|         | 6.1 Fischer's Mutual Exclusion Protocol                      | 52 |

|         | 6.2 A Railway Control System                                 | 53 |

| 7       | Conclusion                                                   | 55 |

31

|    | Refe           | erences                                                   |     | . 56  |

|----|----------------|-----------------------------------------------------------|-----|-------|

| Pa | $\mathbf{per}$ | B: Compositional and Symbolic Model-Checking of Real-     | Tir | ne    |

|    | $\mathbf{Sys}$ | tems                                                      |     | 59    |

|    | 1              | Introduction                                              |     | . 61  |

|    | 2              | Real-Time Systems                                         |     | . 63  |

|    |                | 2.1 Timed Transition Systems                              |     | . 63  |

|    |                | 2.2 Networks of Timed Automata                            |     | . 64  |

|    | 3              | A Logic for Safety and Bounded Liveness Properties        |     | . 67  |

|    |                | 3.1 Syntax and Semantics                                  |     | . 67  |

|    |                | 3.2 Derived Operators                                     |     | . 68  |

|    | 4              | Symbolic Model-Checking                                   |     | . 69  |

|    |                | 4.1 Operations on Clock Constraints                       |     | . 70  |

|    |                | 4.2 Model-Checking by Constraint Solving                  |     | . 71  |

|    |                | 4.3 Implementation Issues                                 |     | . 73  |

|    | 5              | Compositional Model-Checking                              |     | . 75  |

|    |                | 5.1 Quotient Construction                                 |     |       |

|    |                | 5.2 Minimisations                                         |     | . 78  |

|    | 6              | Conclusion and Future Work                                |     | . 81  |

|    | Refe           | erences                                                   |     |       |

| Pa | per            | C: Diagnostic Model-Checking for Real-Time Systems        |     | 85    |

|    | 1              | Introduction                                              |     |       |

|    | 2              | Real-Time Systems                                         |     |       |

|    | -              | 2.1 Timed Transition Systems                              |     |       |

|    |                | 2.2 Networks of Timed Automata                            |     |       |

|    | 3              | A Logic for Safety and Bounded Liveness Properties        |     |       |

|    | 4              | Diagnostic Model-Checking                                 |     |       |

|    | т              | 4.1 Clock Constraints                                     |     |       |

|    |                | 4.2 Model-Checking with Diagnostic Synthesis              |     |       |

|    |                | 4.3 Towards an Algorithm                                  |     |       |

|    |                | 4.4 An Example: Fischer's Mutual Exclusion Protocol       |     |       |

|    | 5              | Applications                                              |     |       |

|    | 0              | 5.1 UPPAAL                                                |     |       |

|    |                | 5.2 Philips Audio-Control Protocol                        |     |       |

|    | 6              | Conclusion and Future Work                                |     |       |

|    |                | erences                                                   |     |       |

|    | A              | The System Descriptions                                   |     |       |

|    | В              | Proof of Theorem 4.1                                      |     |       |

|    | D              |                                                           | • • | . 107 |

| Pa | -              | D: Efficient Verification of Real-Time Systems: Compact   | Da  |       |

|    |                | uctures and State-Space Reduction                         |     | 109   |

|    | 1              | Introduction                                              |     |       |

|    | 2              | Preliminaries                                             |     |       |

|    |                | 2.1 Timed Automata                                        | ••• |       |

|    |                | 2.2 Difference Bounded Matrices & Shortest-Path Closure . | • • | . 116 |

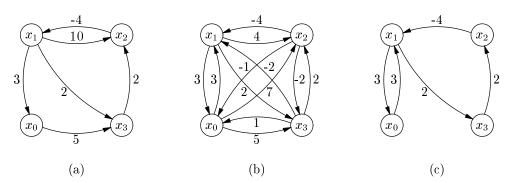

| 3    | Minim  | nal Constraint Systems & Shortest Path Reductions 1 | 17  |

|------|--------|-----------------------------------------------------|-----|

|      | 3.1    | Reduction of Zero-Cycle Free Graphs                 | .17 |

|      | 3.2    | Reduction of Negative-Cycle Free Graphs             | .19 |

| 4    | Globa  | l Reductions and Control Structure Analysis         | .22 |

|      | 4.1    | Potential Space-Reductions                          | .22 |

|      | 4.2    | Control Structure Analysis and Application          | .23 |

| 5    | Exper  | imental Results                                     | .25 |

| 6    | Conclu | usion                                               | .27 |

| Refe | rences |                                                     | .28 |

|      |        |                                                     |     |

# III Case Studies

## 131

| Paper  | E: Automated Analsysis of an Audio-Control Protocol Using                                                                                           |   |

|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------|---|

| Upi    | PAAL 133                                                                                                                                            | 5 |

| 1      | Introduction $\ldots \ldots 135$           | j |

| 2      | Committed Locations                                                                                                                                 | 7 |

|        | 2.1 An Example                                                                                                                                      | 7 |

|        | 2.2 Syntax                                                                                                                                          | 3 |

|        | 2.3 Semantics                                                                                                                                       | ) |

| 3      | Committed Locations in UPPAAL                                                                                                                       | ) |

|        | 3.1 The Model-Checking Algorithm                                                                                                                    | ) |

|        | 3.2 Space and Time Performance Improvements                                                                                                         | ) |

| 4      | The Audio Control Protocol with Bus Collision                                                                                                       | 3 |

| 5      | A Formal Model of the Protocol                                                                                                                      | F |

| 6      | Verification in UPPAAL                                                                                                                              | 7 |

| 7      | Conclusions                                                                                                                                         | ) |

| Refe   | erences                                                                                                                                             | ) |

| А      | The System Description                                                                                                                              | L |

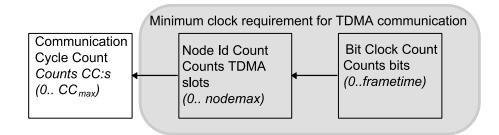

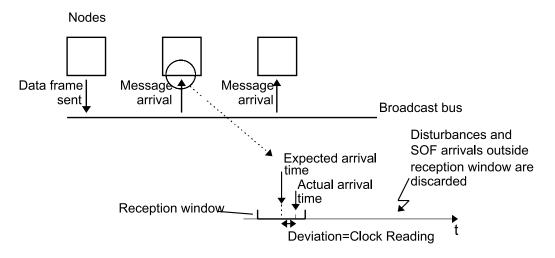

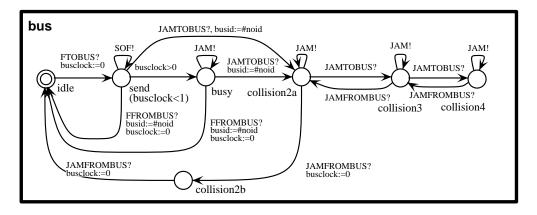

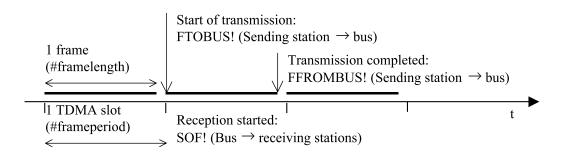

| Donor  | F: Formal Verification of a TDMA Protocol Startup Mechanism 157                                                                                     | 7 |

| r aper | Introduction                                                                                                                                        |   |

| 2      | Protocol Description                                                                                                                                |   |

| 2      | 2.1       General       General       160                                                                                                           |   |

|        | 2.1         General                                                                                                                                 |   |

|        | 2.3 TDMA Time Slot Synchronisation                                                                                                                  |   |

| 3      | Formal Description of the Protocol                                                                                                                  |   |

| 0      | 3.1 Assumptions                                                                                                                                     |   |

|        | 3.2         The System Model         16         16                                                                                                  |   |

| 4      | Verification $\ldots \ldots \ldots$ |   |

| -      | 4.1 Correctness Properties                                                                                                                          |   |

|        | 4.2         Duration of Start-Up         1         1         168                                                                                    |   |

| 5      | •                                                                                                                                                   |   |

|        | erences $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $170$                                                                                          |   |

| A      |                                                                                                                                                     |   |

|        | Conclusions                                                                                                                                         | ) |

| А      | Appendix                                                                                                                                            | L |

| 1 Introduction $\ldots$ |       | 1 1 1 1 |

|----------------------------------------------------------------------------------------------------------|-------|---------|

|                                                                                                          |       | 175     |

| 2 A Logic for Safety and Bounded Response Time Properties                                                |       | 176     |

| 2.1 Timed Transition Systems and Timed Traces                                                            |       | 177     |

| 2.2 The Logic: Syntax and Semantics                                                                      |       | 177     |

| 3 Verifying Bounded Response Time Properties by Reachability Ana                                         | lysis | 179     |

| 4 The Gear Controller                                                                                    |       | 182     |

| 4.1 Functionality                                                                                        |       | 182     |

| 4.2 Requirements                                                                                         |       | 183     |

| 5 Formal Description of the System                                                                       |       | 184     |

| 6 Formal Validation and Verification                                                                     |       | 186     |

| 6.1 Requirement Specification                                                                            |       | 186     |

| 7 Conclusion                                                                                             |       | 188     |

| References                                                                                               |       | 189     |

| A The System Description                                                                                 |       | 191     |

# Part I Introduction

# 1 Background

In this thesis, I shall present the past five-years of research behind the following quotation:

"In 1996, Bengtsson and his colleagues model checked the entire protocol, thus completing the quest of fully automating a human proof that as little as two years ago was considered far out of reach for algorithmic methods."

E.M. Clarke and J.M. Wing, Formal Methods: State of the Art and Future Directions, ACM Computing Surveys, Vol. 28, No. 4, 1996, page 631.

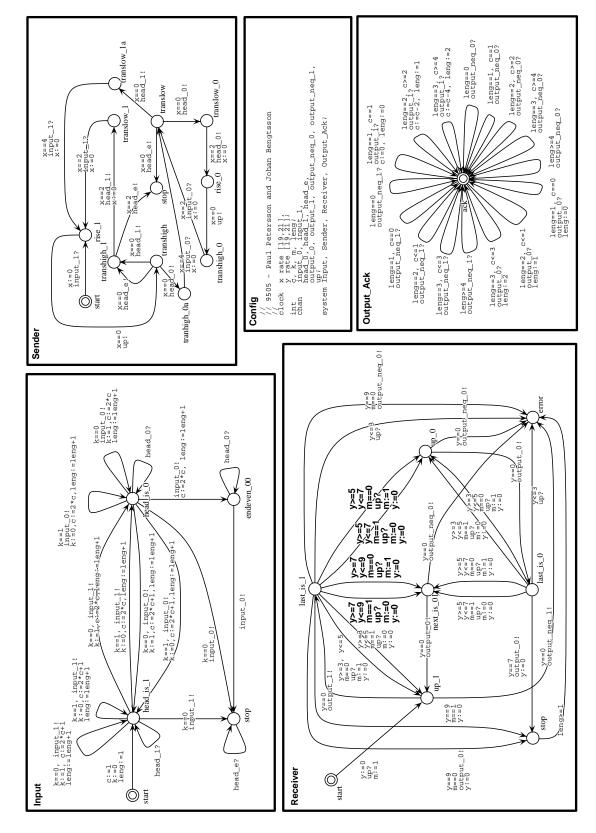

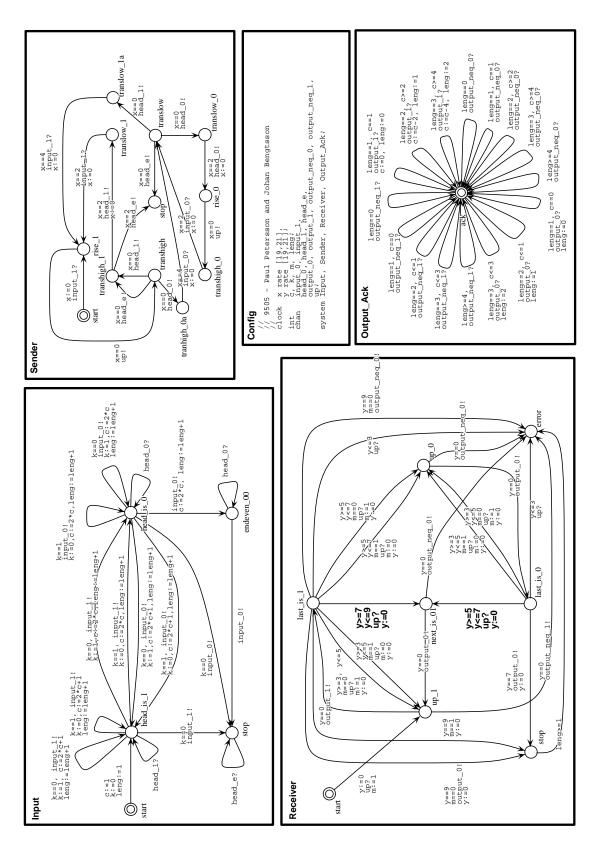

First, we notice that "Bengtsson and his colleagues" refers to paper E included in this thesis. It reports an automated analysis of an audio-control protocol developed by Philips. The protocol is used in Philips audio and TV equipments for transferring control-information between components. For example, an amplifier can use the protocol to transfer information about which buttons are being pressed on the remote control to a connected CD-player.

The protocol by Philips is just one example of how information technology, i.e. the use of computers to create, store, exchange, and use information, has become a part of our everyday life. In fact, we trust computers to control much more safetycritical equipments than just audio and TV sets. For example, we use computer based systems to control anti-lock braking systems in cars, railway switching systems, banking systems, complex production processes, nuclear power plants, and military systems such as missiles [BW90, But97]. In most of these applications computer failures can lead to economical damage, environmental catastrophes, and in some cases, loss of human lives.

Over the past decades, it has been a challenge for computer scientists to develop theories and techniques that guarantee that computer systems operate correctly, i.e. according to prescribed specifications expressing their desired behaviour. The traditional ways of obtaining such "guarantees" have been simulation and testing. However, in many applications this process is exceedingly time-consuming and often provides only probabilistic measures of correctness.

In the literature, a great number of mathematically based techniques for reasoning about the correctness of computer systems have been proposed [Hoa69, Dij75, Pnu77, Lam77, Hoa78, Mil89, Hol91]. The general idea is to describe the computer system under consideration in a formal framework, and then apply rigorous methods to *prove* that the system description is correct in the sense that it satisfies certain formally specified requirements. The advantage of this approach is that it can be used early in the design cycle to detect logical design bugs even before they have been implemented. However, the major drawback is that large formal system descriptions often tend to become complex and are therefore generally considered difficult to analyse [WT94].

To overcome this problem, techniques have been sought to analyse formal system descriptions automatically. One of the most promising approaches has been *model* checking [CE81, QS82, BCM<sup>+</sup>90, ACD90, Hol91, CW96]. In contrast to manual techniques, model checking is completely automatic in the sense that the proof showing that a system satisfies a given requirement is automatically generated.

In this thesis we shall study and develop model-checking techniques and tools for a special class of computer systems known as *real-time systems*. The audio-control protocol by Philips mentioned earlier is a typical example of such a system.

## 1.1 Real-Time Systems

A real-time system is a computer system whose correctness depends not only on the output, but also the time at which the output is produced. In fact, the examples we have mentioned so far are all real-time systems according to this definition. Consider for example an anti-lock brake system in a modern vehicle. Sensors provide it with information of the current wheel speed and it must react in a timely fashion when the driver applies the brake. If it does not react timely, it is not correct and will probably be of more harm than help to the driver.

The class of real-time system includes many *embedded* and *safety-critical system* that are subcomponents of a larger complex system operating in safety-critical environment [Sto96]. These systems are often known as *hard* real-time as they must always react timely, as opposed to *soft* real-time systems that may occasionally fail to meet their timing requirements [TH96]. A common characteristics of real-time systems is that they may consist of many components operating in parallel; they are then known as *concurrent systems*. As real-time system must react to every stimuli from the environment, they are also called *reactive systems* [Pnu86].

The term "real-time" is sometimes used for systems that react to external inputs as *quickly* as possible. Our definition requires the reaction to be *timely* in the sense that the system should react according to timing constraints. To reason about these systems we therefore need to define the meaning of precise timing more carefully. We shall assume a global time scale that is a time reference for both the system and its environment. A time scale indicates that time can be measured. However it does not imply a global clock in the system. The components of a real-time system may have their own clocks. Conceptually, these clocks can be considered as the local clocks of the components, which can be tested and reset. The components may communicate via channels. However, we shall only consider a simple form of synchronisation, namely handshaking that has been implemented by the rendezvous mechanism in many programming languages for real-time systems e.g. Occam 2 and Ada [Bar94], and in formalisms such as CSP [Hoa78] and CCS [Mil89].

This thesis will be focused on developing efficient techniques for analysing the behaviours of real-time systems. We first introduce a well developed model that we shall use to describe such systems.

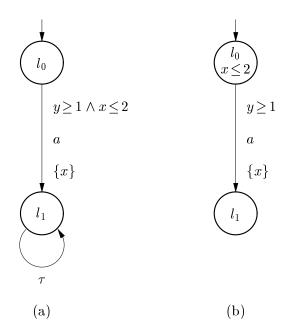

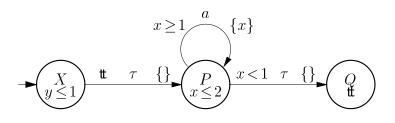

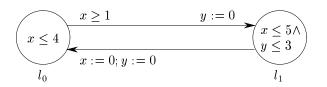

Figure 1: Two Timed Automata.

## 1.2 Timed Automata

There have been many formalism description techniques introduced in the literature for describing time-constrained systems [DS89, NRJV90, Yi91, Han91, AH92, AL92, BD91, Rok93, AD90, ACD90, Dil89, Hen91, Nan92, ACHH93]. One of the most successful formalisms is the model of timed automata [AD90, ACD90, HNSY92, NSY92a].

The model of timed automata was first introduced in 1990 by Alur and Dill [AD90] as an automata-theoretic approach for describing and analysing the behaviour of finite-state systems with real-valued clocks. In the following we outline the two first proposed models, timed graphs [ACD90] and timed Büchi automata [AD90], and compare them with a later proposed variant, called timed safety automata [HNSY92]. We also briefly introduce the model, networks of timed automata, which we shall work with in this thesis.

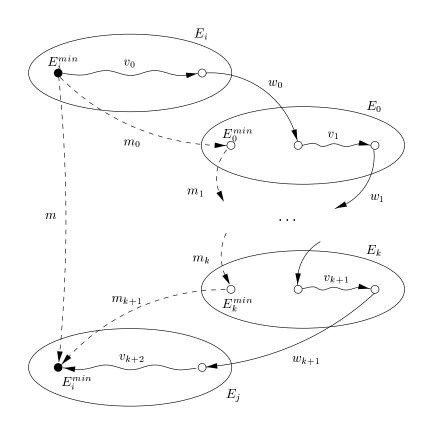

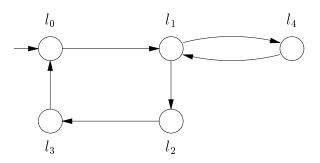

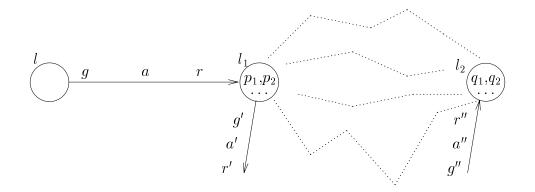

#### Timed Graphs

The model of *timed graphs* extends the model of finite-state automata with a finite collection of real-valued clocks [ACD90]. The clocks proceed synchronously (i.e. at the same rate) and measure the time since they were last reset. Syntactically, the edges of timed graphs are labeled with action names as in finite-state automata, but extended with clock constraints to test the clock values, and reset sets indicating the assignment of the clock values to zero. As an example consider the timed graph shown in Figure 1(a). It has two clocks, x and y, two control locations  $l_0$  and  $l_1$ , and an *edge* from control location  $l_0$  to  $l_1$  labeled with the guard  $y \ge 1 \land x \le 2$ , the action name a, and the reset set  $\{x\}$ .

A state of a timed graph is in the form (l, v), where l is a control location and v is an assignment mapping clock variables to non-negative real numbers. To introduce the semantics of timed graphs we reconsider the timed graph shown in Figure 1(a). Assuming that all clock variables are initially set to zero and the initial control location is  $l_0$ , the graph starts in the state  $(l_0, \{x = y = 0\})$ . As the clocks increase synchronously with time, it may evolve to all states of the form  $(l_0, \{x = y = t\})$ , where t is a non-negative real number. At any state with  $t \in [1, 2]$  it may change to state  $(l_1, \{x = 0, y = t\})$  by following the edge from  $l_0$  to  $l_1$ , that resets x. However, it can also idle forever in location  $l_0$  since there is no way of forcing progress in the semantics of timed graphs. Note that in the literature the notion of timed graphs is often known as timed automata.

#### Timed Büchi Automata

A Büchi automaton [Büc62] is a finite-state automaton with a subset of its states being accepting states. Only transition sequences with infinitely many accepting states are considered valid (i.e. accepting) runs of a Büchi automaton.

Timed Büchi automata [AD90] are Büchi automata extended with clocks in the same way as in timed graphs, but timed Büchi automata accept infinite runs only, in the above sense. As an example, we reconsider the timed automaton shown in Figure 1(a), but now interpreted semantically as a timed Büchi automaton. Assuming  $l_1$  is the only accepting location in the automaton, all valid runs must pass through location  $l_1$  infinitely often. Note that this implies that the automaton, in all valid runs, leaves location  $l_0$  within 2 time units (but not before 1 time unit), as the guard  $x \leq 2$  is false at any later time point. Thus, in the example and in general, the Büchi acceptance condition imposes implicit progress conditions on the control locations, since only the set of valid runs is considered when the behaviour of an automaton is analysed.

#### **Timed Safety Automata**

In contrast to the Büchi accepting condition which is a theoretically elegant way to impose progress conditions on locations in timed automata, there have also been other suggestions to specify progress conditions [HNSY92, NSY92a]. Timed safety automata, due to Henzinger et.al. [HNSY92], are timed automata without the acceptance condition. Instead, each location is labeled explicitly with a local progress condition in the form of a clock constraint, called a *location invariant*. Semantically, the location invariant is required to always hold when the automaton operates in the location and consequently the automaton must change location while the location invariant still holds. As an example, consider the timed safety automaton shown in Figure 1(b). It is similar to the timed Büchi automaton shown in Figure 1(a) in the sense that it must advance from location  $l_0$  within 2 time units according to the location invariant.

We believe that the notion of local progress conditions in the form of location invariants is more appealing for modelling and automated analysis than the more complex Büchi accepting condition. We shall therefore use timed automata with location invariants to model real-time systems.

#### Networks of Timed Automata

The systems we are interested in often consists of several communicating components executing in parallel. The problem of how to describe such systems is not explicitly addressed in the early work on timed automata [AD90, ACD90, HNSY92]. In [AD90], the parallel composition of timed automata is interpreted as logical conjunction, which is similar to the strong (multi-) synchronisation operator from process algebras, defined by the rule:

$$\frac{A \Leftrightarrow^{a} A' \qquad B \Leftrightarrow^{a} B'}{A \& B \Leftrightarrow^{a} A' \& B'}$$

Intuitively, it means that the whole system described by A & B may make a move (i.e. do an a) only if the components described by A and B can do the same (and at the same time). That is, all components of a composed system must synchronise on every action at every time point.

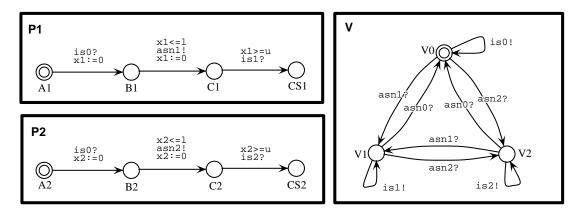

This seems to be too strong a restriction for applying timed automata in practice. Therefore, we shall instead work with networks of timed automata. A network of timed automata is simply the parallel composition  $A_1 | \cdots | A_n$  of a finite collection  $A_1, \ldots, A_n$  of timed automata for a given synchronisation function |. In particular, we will use networks of timed automata composed with a CCS-like parallel composition operator [Mil89]. It allows for individual components to perform internal actions (i.e. interleaving), and for pairs of components to synchronise on actions.

## **1.3** Automatic Verification

The act of *verification* is that of using mathematically justified methods to prove that a formal system description satisfies certain desirable properties. In this thesis we are mainly concerned with *algorithmic* verification techniques where the property of interest is checked automatically, as opposed to techniques that require manual assistance. In particular, we shall develop *model-checking* algorithms for timed systems. Such algorithms determine if a desired property, formalised as a logical formula, is satisfied by a system model.

#### Safety Properties

To specify and reason about the correctness of untimed computer programs, logics have been very successful, e.g. pre- and postcondition pairs formulated in Hoare's logic have been used for sequential programs [Hoa69], and temporal logics for concurrent systems [Pnu77]. In recent years, several timed variants of these logics have also been developed for specifying real-time properties, see e.g. [AH92] for an overview.

In [Lam77], Lamport classifies temporal properties into *safety* and *liveness* properties. Intuitively, a liveness property asserts that "something good" eventually will happen, and a safety property that "something bad" should never happen [Lam80].

In this thesis, we shall restrict ourselves to studying safety properties only. This means that there are some properties that we will not be able to specify and verify<sup>1</sup>. However, there are several arguments in favour of the restriction in the context of real-time systems.

First, real-time systems are often embedded in safety-critical environments. It has therefore been argued that the practical goal of verifying real-time systems is often to show that "something bad" never happens [Hal93]. That is, to ensure that the system is "safe", which can be expressed as a set of safety properties.

Secondly, it is possible to formulate a form of liveness, known as *bounded liveness*, with safety properties according to Lamport's classification [Lam77]. Intuitively, a bounded-liveness property asserts that "something good" happens within a specified time bound. As we are concerned with systems that are required to operate under timing-constraints, it is even more interesting to reason about bounded liveness than unbounded liveness, e.g. some event will eventually occur in the future.

Finally, in choosing specification languages and verification algorithms there is a trade-off between *expressiveness*, i.e. which properties can be specified, and *complex-ity*, i.e. how difficult properties are to verify [Hen91]. In general it is possible to find more efficient algorithms for logics with restricted expressiveness. Safety properties can be verified by reachability analysis algorithms that examine all possible states of a system to ensure that "something bad" never happens. This has been used to develop efficient algorithms for finite automata. For timed automata however, the state-space is infinite because of the real-valued clocks; but it is possible to represent the infinite state-space by finite partitioning due to the region-graph construction technique [AD90].

#### **Region-Graph Construction**

In the first papers about timed automata it is shown that fundamental verification problems associated with the model, such as language emptiness and model-checking of timed temporal logic formulae, are decidable [AD90, ACD90]. The result is obtained by constructing a finite-state system called a *region graph*. In a region graph, each region essentially consists of the set of concrete states that are equivalent, in the sense that they can evolve to the same regions in the future.

Based on Alur and Dill's pioneer work, several other algorithms were developed for the verification problems associated with the model, e.g. [ACD90, Nan92, Cer92]. However, in practice these algorithms are often computationally infeasible because of the huge size of the region graph. The region graph grows exponentially, not only in the number of automata and the number of clock variables, but also in the largest integer constant used in the clock constraints of the automata.

#### Symbolic Verification Algorithms

Subsequently, techniques have been sought to develop algorithms that perform better in practice, in the sense that they run faster and consume less space on the instances

<sup>&</sup>lt;sup>1</sup>For example, we will not be able to reason about zeno-properties [AL92].

of timed automata that appear when realistic systems are modelled. One way to develop such algorithms have been to use coarser and consequently more compact abstract representations of the state-space [Dil89, HNSY92, ACHH93, Hal93]. We shall call such algorithms *symbolic* since the term has been used in the literature on verification of timed systems<sup>2</sup>. It should be noticed that the region-graph technique is also a symbolic technique.

The first progress in the development of symbolic model-checking algorithms for timed automata is presented in [HNSY92]. A symbolic model-checking algorithm is described that partitions the concrete state-space into equivalent classes, in such a way that states within each class are equivalent with respect to the investigated automaton and the property currently being checked. Though the algorithm in the worst case will construct (the equivalent of) the full region-graph, it often yields a coarser and smaller partitioning. In practice, the algorithm is insensitive to the maximal integer constant appearing in the clock constraints of the automata and the checked property. However, it is still very sensitive to the number of automata in the analysed system as the product of the automata is constructed before verification is performed.

#### **On-the-Fly State-Space Generation**

An on-the-fly verification algorithm constructs the state-space of the investigated system and verifies the property of interest simultaneously, in contrast to the traditional approach of generating the whole state-space before verification. This allows the verification to be stopped when the truth-hood of the verified property has been determined. On-the-fly techniques therefore often require a relatively small part of the whole state-space to be investigated.

Several on-the-fly verification algorithms have been developed for finite-state systems in the literature, e.g. [VW86, Hol91]. In this thesis, we shall investigate how on-the-fly techniques can be adopted to verification algorithms for real-time systems to deal with the exponential growth of the state-space caused by the number of automata in parallel systems. Moreover, we shall investigate the possibility of combining on-the-fly techniques with symbolic verification techniques to develop algorithms that are less sensitive to the number of automata and insensitive to the constants appearing in the clock constraints of the analysed automata.

#### **Compositional Verification**

The notion of *compositional verification* in general relates to methods for splitting up the verification of a combined system into verifications of its components. This means that a compositional verification technique shows that a system satisfies properties without investigating the product of the whole system, but rather its components one by one.

$<sup>^{2}</sup>$ In the context of verification techniques for finite-state systems, the term "symbolic" is often used for non-enumerative methods of state-space representation and exploration, such as Binary Decision Diagrams (BDD's) [Bry86, BCM<sup>+</sup>90].

For untimed systems a number of compositional verification techniques have been described in the literature, e.g. [OG76, Sti86, Lar86, Jon87, And95]. In this thesis, we shall develop compositional verification algorithms for real-time systems, based on a compositional model-checking technique for untimed concurrent systems, known as *quotienting*, introduced by Larsen [Lar86] and further studied by Andersen [And95]. The technique avoids exploring the whole state-space of a composed system by gradually moving components from the system description to the specification.

An initial attempt to transfer Andersen's result to a real-time setting is reported in [LL95]. This work also contains some experimental evidence showing the potential of the quotienting technique for real-time systems. However, the result in [LL95] is obtained by using the region-graph technique.

# 2 Summary of Results

In this section we summarise the main contributions of this thesis. The presentation is divided into four areas: symbolic verification algorithms, memory usage reductions, verification tool developments, and case studies.

## 2.1 Symbolic Verification Algorithms

#### On-the-Fly Verification (Papers A and B)

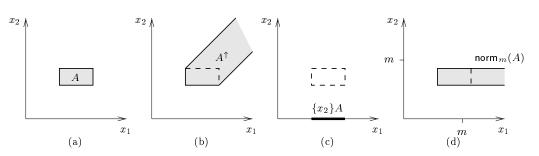

A reachability analysis algorithm for verifying safety properties of networks of timed automata is developed in paper A. In contrast to previously proposed algorithms for timed automata, ours operates in an on-the-fly manner. That is, it verifies properties during state-space exploration, instead of constructing and representing the whole state-space before the checking. The algorithm is also symbolic in the sense that the infinite state-space is finitely partitioned into subsets that are represented and manipulated using a class of linear constraints, known as *difference bound matrices* (DBM) [Bel57, Dil89]. To develop the algorithm, we give a finite symbolic semantics of timed automata, which is defined as a transition system with transition rules given in terms of predicates and operations on constraints. This means that we reduce the verification problem of timed automata to that of manipulating and solving simple constraints.

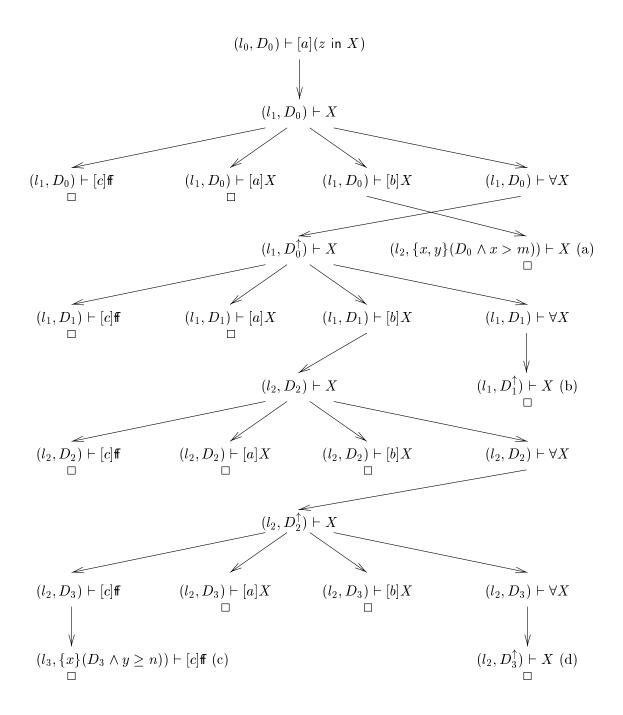

In paper B these results are applied to develop a symbolic and on-the-fly modelchecking technique for checking a simple timed modal logic  $\mathcal{L}_s$  to express safety and bounded liveness properties. The logic can be seen as a fragment of the timed modal  $\mu$ -calculus (T<sub>µ</sub>) [HNSY92]. Though it is comparatively less powerful than e.g. T<sub>µ</sub> and TCTL [ACD90], our logic is still sufficiently powerful for practical purposes; a claim we substantiate by showing that a number of operators of other real-time logics can be expressed as derived operators in  $\mathcal{L}_s$ . Most importantly, the somewhat restrictive expressive power of  $\mathcal{L}_s$  allows us to apply on-the-fly and constraint-solving techniques to develop an efficient model-checking algorithm for timed automata.

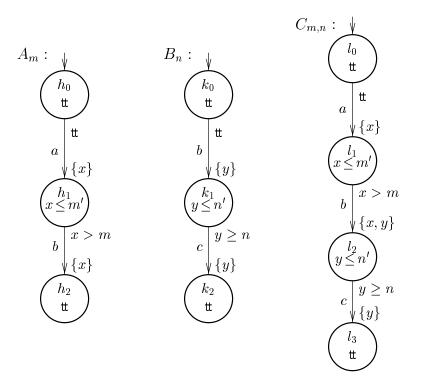

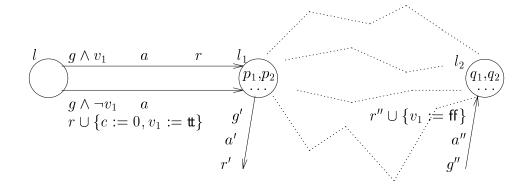

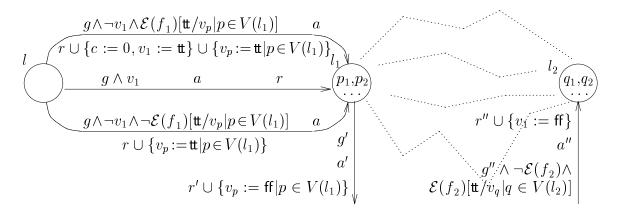

## Compositional Verification (Paper B)

In paper B, we present a symbolic and compositional verification technique for checking  $\mathcal{L}_s$ -formulae of networks of timed automata. It extends quotienting for (untimed) finite-state systems [And95] to real-time systems where subsets of the infinite statespace are manipulated symbolically using constraint-solving techniques. This means that the presented technique confines both the exponential blow-up in the statespace caused by the number of components, and the exponential growth caused by the number of clocks.

Like the quotienting technique for finite-state systems [Lar86, And95], ours solves the model-checking problem without exploring or even generating the state-space of the automata network. Instead, timed automata are gradually moved from the system description to the requirement specification. More precisely, given the modelchecking problem  $(A|B) \models \varphi$ , where (A|B) is the system to be verified, with the two timed automata A and B, and  $\varphi$  is a  $\mathcal{L}_s$ -formula, the quotienting technique shows how to construct the quotienting formula  $\varphi/B$  such that

$$(A|B) \models \varphi$$

if and only if  $A \models (\varphi/B)$

Repeating this processes yields the equivalent model-checking problem  $\models ((\varphi/B)/A)$ . Thus, roughly speaking the quotienting technique transforms the model-checking problem to that of checking the truth-hood of the quotienting formula  $((\varphi/B)/A)$ .

## 2.2 Memory Usage Reduction

In papers D and E, we present three techniques to reduce the memory usage of realtime verification algorithms. Note that the techniques are orthogonal and can thus be applied in combination.

## Control Structure Reduction (Paper D)

An on-the-fly technique to reduce the space-consumption of reachability analysis algorithms for timed automata is described in paper D. The technique is based on the observation that not all symbolic states encountered during state-space exploration, but only certain critical symbolic states, need to be saved to ensure termination. Before reachability analysis, the control structure of the automata in the network are statically analysed. Based on this information we are able to compute, in an on-the-fly manner, a set of symbolic states to save, that is sufficient for guaranteeing termination of the reachability analysis algorithm. The set of saved symbolic states may not be minimal but the reduction technique performs well in practice. In an experiment with an implementation of the control structure reduction technique in the tool UPPAAL we found that for six examples from the literature, the space-saving is between 13% and 72%.

## Compact Data Structures for Constraints (Paper D)

In paper D we also present a compact data structure for difference bounded matrices (DBM) [Bel57, Dil89, BL96], the class of constraints that arises during symbolic

verification of timed automata. The data structure is based on an  $\mathcal{O}(n^3)$  reduction algorithm that, given a constraint system with *n* clocks, constructs an equivalent reduced system with the *minimal* number of constraints. The reduced system is *canonical* in the sense that two constraint systems with the same solution sets reduce to identical constraint systems. The reduction algorithm is essentially a minimisation algorithm for weighted directed graphs, which extends the transitive reduction algorithm of [AGU72] to weighted graphs.

The space usage of a reduced constraint system is in the same order as for an ordinary DBM, i.e.  $\mathcal{O}(n^2)$ , but it often turns out to be much less in practice. We have tested compact data structures for constraints in an experiment with six examples from the literature. The number of constraints was reduced with 68% to 85%.

### Committed Locations (Paper E)

In paper E we develop the notion of *committed locations*. It allows for atomic behaviours, such as atomic broadcasts, to be accurately modelled in the model of networks of timed automata. More importantly, committed locations are utilised to guide the state-space exploration performed during verification by on-the-fly reachability analysis, to avoid exploring unnecessary interleavings of independent transitions. We present a modified symbolic and on-the-fly reachability analysis algorithm for networks of timed automata which explores and stores a reduced number of symbolic states when committed locations are used. Our experimental results demonstrate significant time and space-savings of the modified model-checking algorithm when committed locations are used.

## 2.3 Verification Tool Development

The two verification tools TAB and UPPAAL have been developed based on the techniques and algorithms presented in this thesis.

#### The TAB Tool (Paper A)

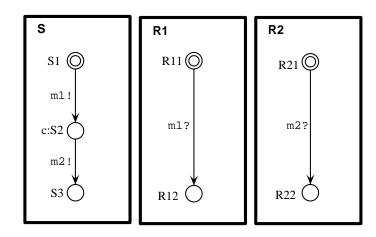

TAB is the first prototype of UPPAAL developed in 1993 at Uppsala University. It is written in Prolog and the general constraint solver PCS (Prolog Constraint Solver) [Nil93]. The implementation is based on the symbolic and on-the-fly reachability analysis algorithm developed in this thesis. Although the TAB tool is a prototype, it has successfully been applied to automatically verify safety properties of some non-trivial examples, including a version of Fischer's mutual exclusion protocol and a railway control-system. These examples, as well as the theoretical foundations of the tool TAB are presented in paper A.

#### The UPPAAL Tool (Papers A, B, C, D and E)

UPPAAL (UPPsala and AALborg) is a suite of tools for modelling, validation and verification of real-time systems, developed in collaboration between Uppsala University and Aalborg University since 1995 [LPY97a, BLL<sup>+</sup>98]. The modelling language in

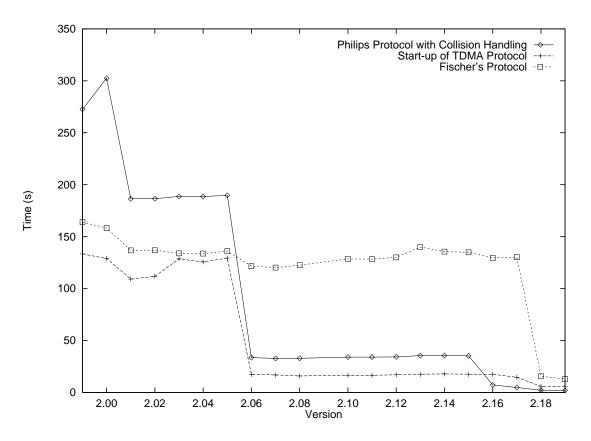

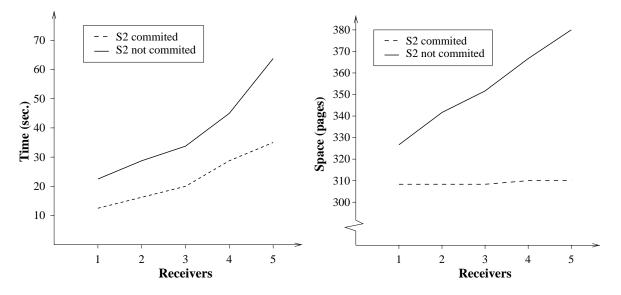

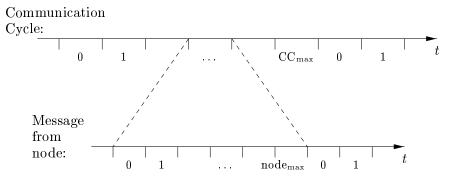

Figure 2: Time benchmarks (in seconds) for UPPAAL version 1.99–2.19. Version 1.99 and 2.19 are dated December 1996 and September 1998 respectively.

UPPAAL is networks of timed automata extended with data variables with finite domains, and arrays of such variables. The verification engine is based on the on-the-fly and symbolic constraint solving techniques presented in this thesis.

In contrast to its predecessor TAB in which all constraint solving is implemented in PCS, the constraint operations in UPPAAL are implemented entirely in  $C^{++}$  based on DBM [BL96]. To further improve the performance, the notion of committed locations as well as the control structure reduction and the compact data structures for constraints have been implemented. Moreover, a simple but efficient strategy for reuse is applied in the tool [LPY97b]. If possible, when several properties of a system are analysed, the generated portion of the state-space is reused, thus avoiding time-consuming re-computations.

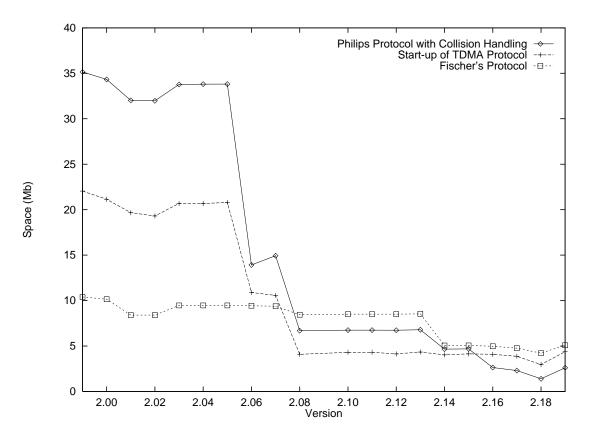

Figure 2 and 3 illustrate how the time and space performance of UPPAAL have improved from version 1.99 to version 2.19 in terms of three examples<sup>3</sup>: a TDMA start-up algorithm, Fischer's mutual exclusion protocol with 5 processes and Philips audio-control protocol with bus collision. In particular, we notice that in both the time and space usage diagrams there is a performance improvement in version 2.06 compared with the proceeding version. This is due to a number of internal improve-

$<sup>^{3}</sup>$ All UPPAAL versions in the test are compiled using GCC 2.7.2.3 and installed on the same Pentium II 375 MHz machine running Redhat Linux 5.1.

Figure 3: Space benchmarks (in Mb) for UPPAAL version 1.99–2.19.

ments in the verifier, including re-implementation of the main data structure for the explored symbolic state-space. The tool Purify played a significant role in these improvements.

Besides efficiency, the main design criterion of UPPAAL has been user-friendliness. To make debugging of system descriptions easier, the verifier has been extended with support for diagnostic traces (see paper C). When the verification of a particular property succeeds (or fails) an example is automatically produced that shows why the property is (or is not) satisfied by the analysed system model. The user-friendliness has been further improved by the development of graphical interfaces for the various components in the tool.

UPPAAL has been successfully applied in many case studies, to model, design and analyse complex real-time systems, see e.g. paper C, E, F and G. The theoretical foundations of UPPAAL are presented in the papers A, B, C, D and E.

## 2.4 Case Studies

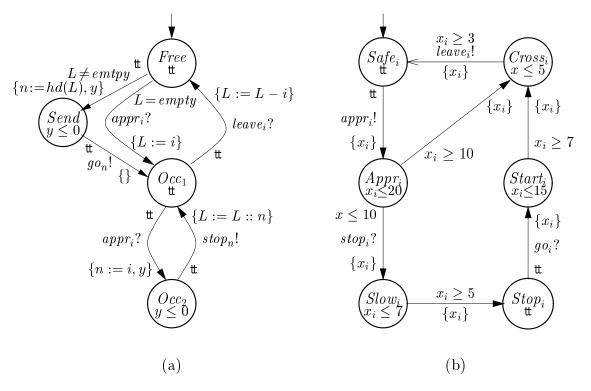

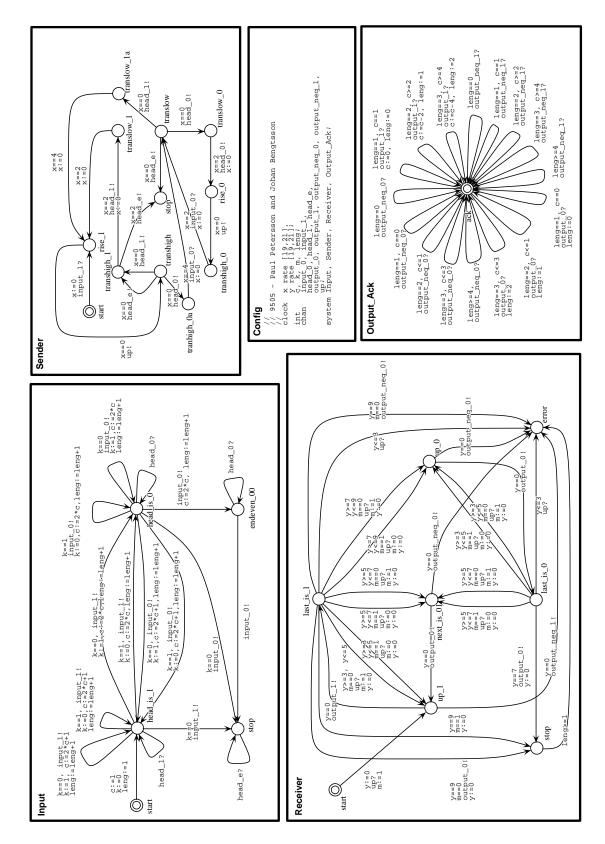

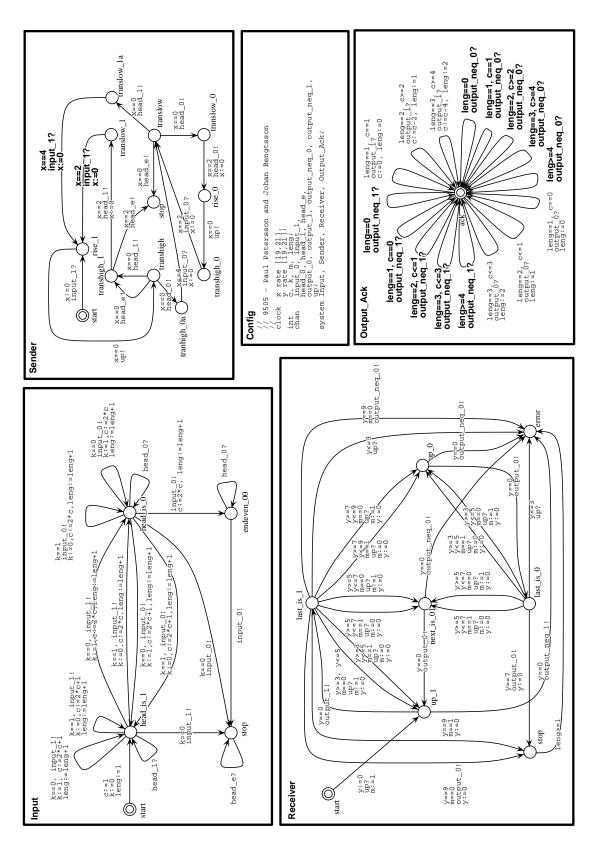

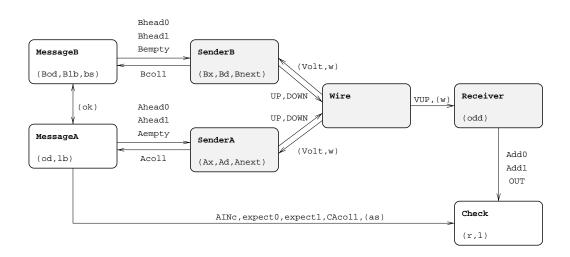

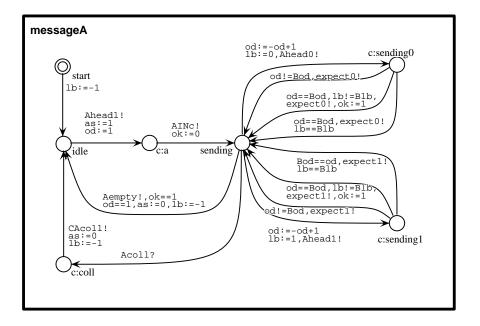

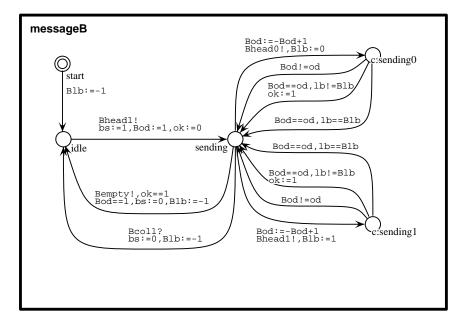

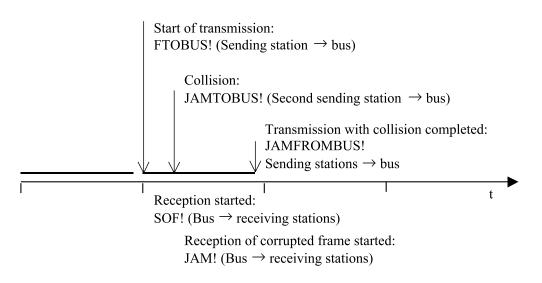

#### Philips Audio-Control Protocol with Bus-Collision Handling (Paper E)

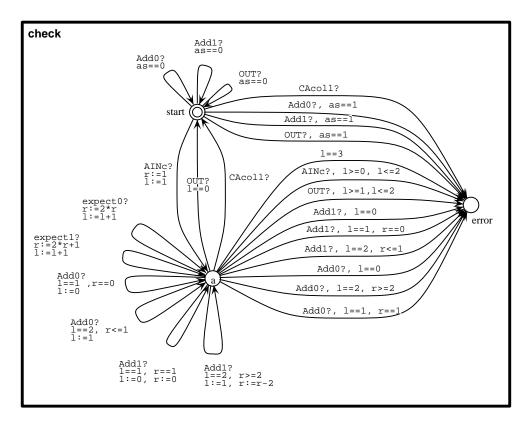

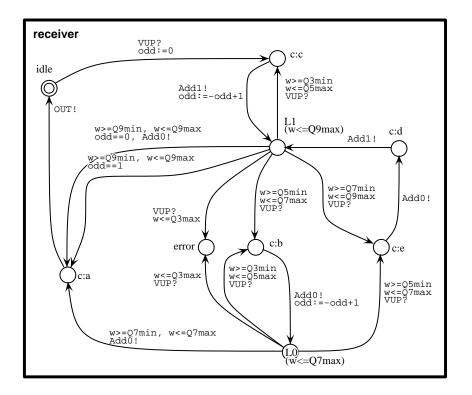

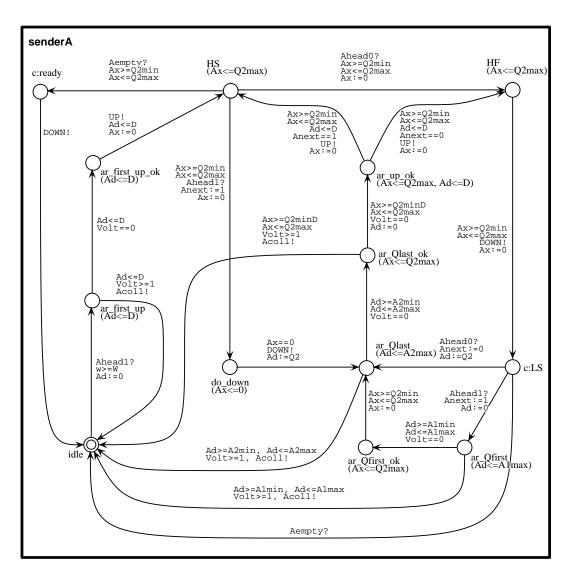

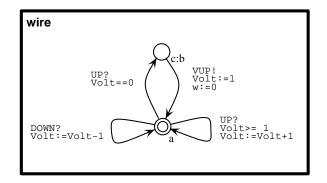

In paper E, we analyse a protocol developed by Philips for the physical layer of a bus protocol connecting the various devices, such as amplifiers and CD-players etc, in audio equipment<sup>4</sup>. A formal description of the protocol is given in the model of timed automata. Four automata are used to model the protocol components and another three automata are used to encode assumptions about its environment and to test its behaviour. As main verification results, we prove using UPPAAL that the protocol model behaves correctly if the error on all timing in the components is bound to  $\pm 5\%$ , and incorrectly if the error is  $\pm 6\%$ . In addition, we model and analyse an erroneous version of the protocol, actually implemented by Philips. Using UPPAAL's ability to generate diagnostic traces when verification fails, we are also able to find and study an error scenario.

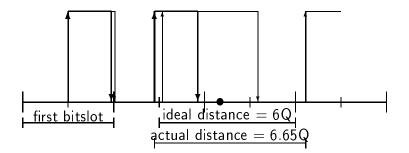

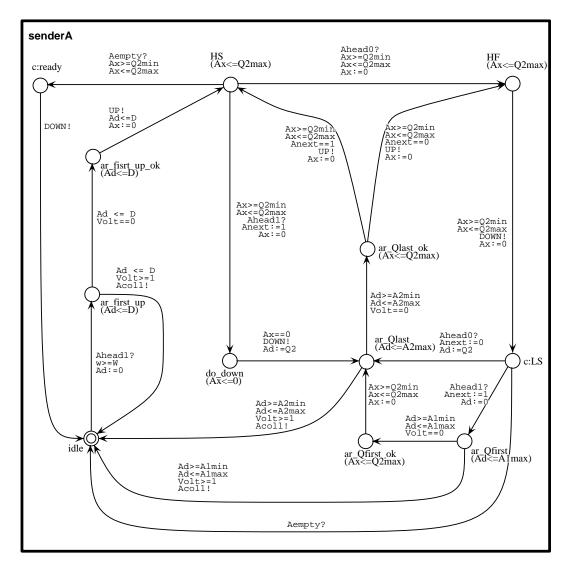

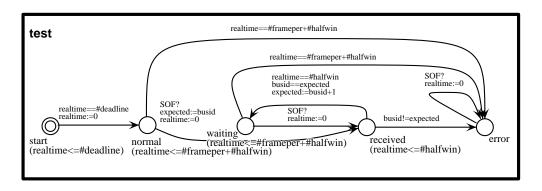

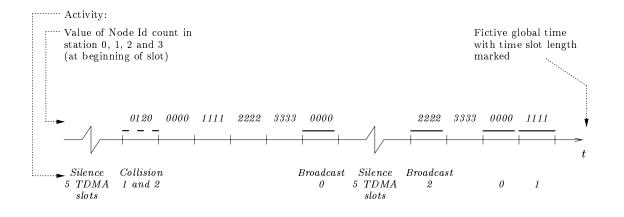

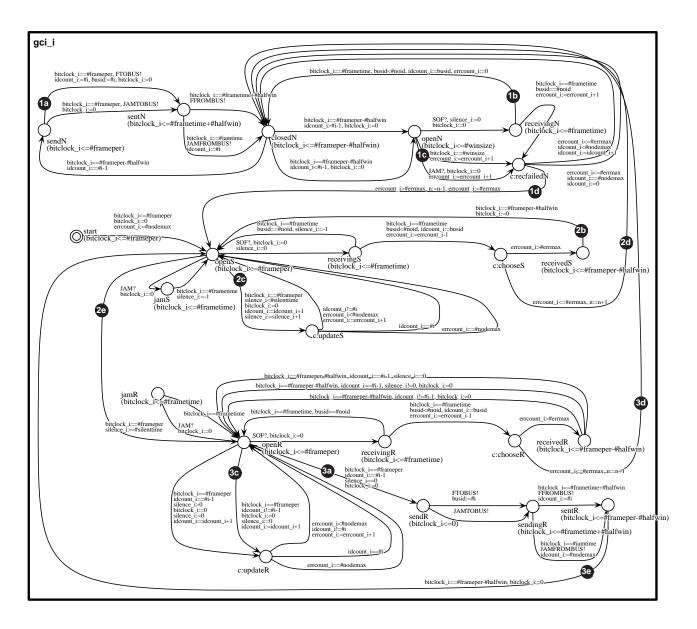

## Start-Up Algorithm of a TDMA Protocol (Paper F)

The start-up algorithm of a time division multiple access (TDMA) based bus protocol is analysed in paper F. The protocol is used in DACAPO [RLST95], a conceptual computer architecture for safety-critical distributed real-time systems. It is intended for physically small distributed systems limited to tens of meters and less than 40 nodes, e.g. operating in modern vehicles. We formally describe the communicating nodes on the bus, and the bus itself, in the model of timed automata. To express correctness properties and assumptions about the protocol, two extra automata are introduced. Using UPPAAL we manage to show that a network of four communicating nodes is guaranteed to become synchronised and operational within a bounded time from an arbitrary initial state, given a clock-drift corresponding to  $\pm 10^{-3}$  between the nodes. Furthermore, we derive an upper time bound for the start-up algorithm to complete, corresponding to 21 TDMA time slots, and describe a discovered worst-case scenario.

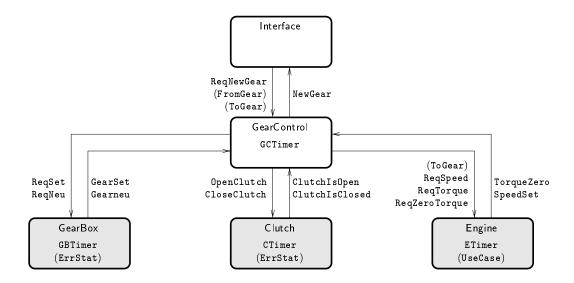

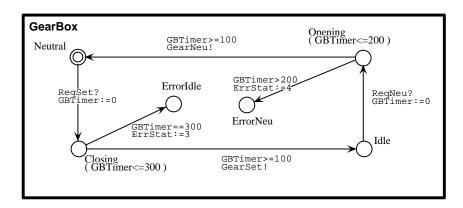

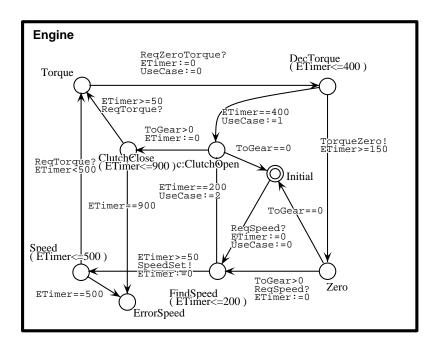

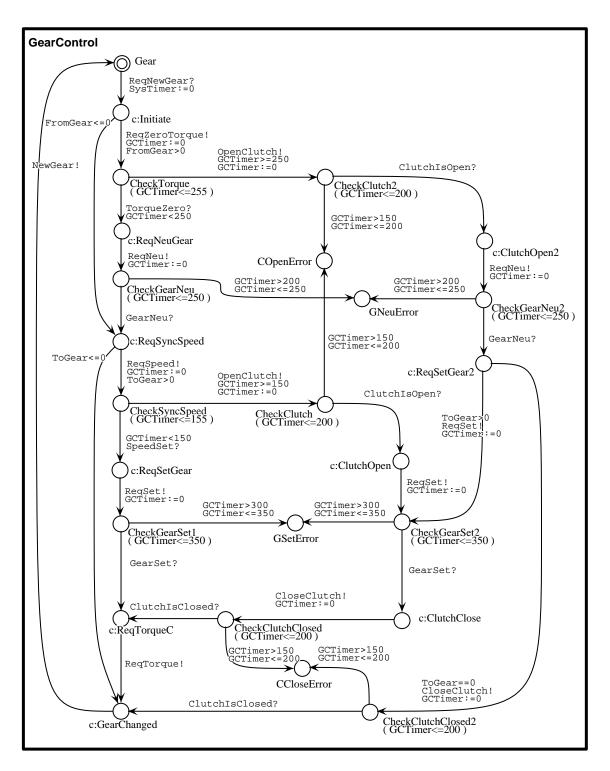

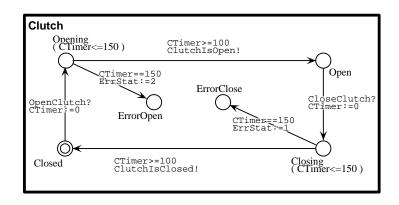

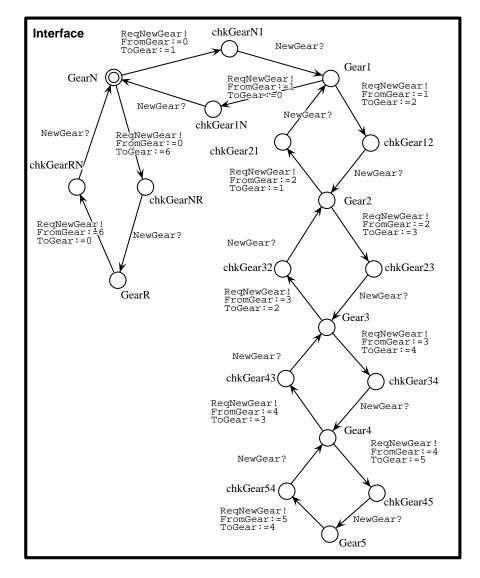

## Gearbox Controller (Paper G)

The gearbox controller is a component in the real-time embedded system that operates in a modern vehicle. In paper G, we presents a case study where UPPAAL is applied to describe and analyse design sketches of a gearbox controller in the early design stages of a project. The controller receives gear-requests from the driver<sup>5</sup> via a communication network and implements the actual gear changes by controlling the involved lower level components, such as the gear, the clutch and the engine. We present a formal description of a gearbox controller, designed from informal requirements prescribed by our industrial partner, the Swedish company Mecel AB. The description, which comprises both a gearbox controller and abstract models of the components in the surrounding environment, is given as a network of five timed automata. We also formally describe Mecel's informal requirements as a set of 47 safety properties. Correctness of the modelled system is established using UPPAAL's simulator to validate the design, and the model-checker to verify that the formal requirements are satisfied.

$<sup>^4\</sup>mathrm{In}$  paper C we analyse a smaller version of Philips audio-control protocol, without bus-collision handling.

<sup>&</sup>lt;sup>5</sup>Gear changes may also be requested by a dedicated component implementing a gear change algorithm.

# 3 Related Work

During the past decade a large number of formalisms for real-time systems have been proposed in the literature, including timed process algebras [DS89, NRJV90, Yi91, Han91, DB96], timed Petri net models [Sif77, BD91, Rok93], real-time logics [AH92, AL92], duration calculus [CHR91], timed automata [AD90, ACD90, HNSY92, AHV93, SV96], and other state based approaches [Dil89, Hen91, Nan92, ACHH93]. In this section we shall only outline work related to timed automata.

## 3.1 Verification of Real-Time Systems

Several algorithms for checking properties of timed automata are described in [HNSY92, KL94, WT94, LL95, SS95, HKV96, Bal96, TC96, BMPY97, BTY97, AJ98, DT98].

In [HNSY92], Henzinger et.al. gives a symbolic model-checking algorithm which iteratively computes the set of (symbolic) states of a timed automata that satisfies a given  $T_{\mu}$ -formula (or TCTL-formula). Whereas the symbolic representation of timing information used in the algorithm is similar as ours; it aims at a much more general framework in the sense that the logic  $T_{\mu}$  is strictly more expressive than  $\mathcal{L}_s$ , the most expressive logic we consider. The restrictive expressive power of our logic allows for efficient model-checking, which has been demonstrated in experiments (see [BLL+95]). Though our logic is restricted it allows to specify invariant and bounded liveness properties that are sufficient for practical purposes.

Wong-Toi presents, in his thesis, a symbolic reachability analysis algorithm for timed automata [WT94]. Its distinguishing feature is to combine symbolic representation of both timing and control information with approximation techniques. To efficiently represent control information he uses *binary decision diagrams* (BDD) [Bry86]. Timing information is symbolically represented with constraints over clocks. Compared with our work, Wong-Toi focuses on finding useful over- and underapproximations techniques to compute super- and subsets of the symbolic state-space respectively. We consider exact verification techniques only.

In [Bal96] Wong-Toi's ideas are further developed by using BDD's also to symbolically represent timing information. The presented algorithm computes, in a more efficient way, an overapproximation of the symbolic state-space<sup>6</sup>. Hence, it can be applied to safely check that undesired combinations of the automata control locations and clock assignments are not reachable in a system model. However, since a superset of the symbolic state-space is computed, the negation can not be checked reliably, i.e. if states are reachable. Furthermore, it should be noticed that overapproximating the state-space can also be more expensive than computing the exact state-space, since in general a super-set of the control-nodes may be generated.

Another symbolic model-checking approach for timed automata based on BDD techniques is presented in [BMPY97]. Roughly speaking, the algorithm uses an extension of BDD's, called *numerical decision diagrams* (NDD's) [AMP97] to represent a discretization of the region graph [GPV94]. Therefore, the algorithm, like the size of the region graph, is very sensitive to the constants used in the clock constraints

<sup>&</sup>lt;sup>6</sup>In fact, algorithms for computing two different overapproximations are presented.

of the analysed timed automata and logical formulae. However, it performs well on systems with small constants, e.g. some instances of Fischer's protocol [BMPY97].

Verification algorithms combining symbolic and on-the-fly techniques for timed automata are presented in [SS95, BTY97, DT98]. In [SS95], the specification language of consideration is an extension of the modal  $\mu$ -calculus for real-time systems, called  $L_{\mu}^{t}$ . Compared with our work, again, a much more expressive logic is considered. As a consequence, the algorithm needs to keep track of more information during verification. It must also gradually refine the symbolic state-space during operation by splitting states into finer partitions. This is not needed in our algorithms since we consider the more restrictive logic  $\mathcal{L}_{s}$ .

Another expressive logic,  $\text{TECTL}_{\exists}^*$ , is considered in [BTY97]. The developed verification algorithm checks for emptiness [AD90, TC96] of the symbolic state-space of possibly several timed automata composed in parallel with the formula, expressed as a (negated) timed Büchi automaton. Emptiness is checked by a standard loop detection algorithm that explores the symbolic state-space of the timed automata using a depth-first strategy. Furthermore, the algorithm uses exactly the same representation of the symbolic state-space as we do. Thus, in comparison with our work, the main difference is that a loop detection algorithm is applied, instead of reachability analysis.

There have also been successful applications of the abstract interpretation framework [CC77] to develop symbolic verification algorithms for real-time systems. In [Hal93], Halbwachs presents an approximative algorithm for checking safety properties of time-constrained reactive systems based on linear relation analysis, an application of abstract interpretation. This work successfully demonstrates the power of the chosen approach, but it is focused on efficiently overapproximating the state-space.

Some results in the area of verification algorithms for Petri net models with time are in fact related to model-checking algorithms for timed automata. In [BD91] an algorithm is presented for verifying reachability, i.e. if a marked place in a safe Petri net is reachable or not. It is based on a symbolic semantics of time Petri nets and linear constraints over clock variables are used to represent timing information. The reachability analysis algorithm of Rokicki [Rok93] for his orbital nets also uses clock constraints. Notably, Rokicki also presents a number of cleverly optimised algorithms for handling clock constraints [Rok93, RM94]. These algorithms are directly applicable in verification algorithms for timed automata that represent clock constraints by difference bound matrices.

## **3.2** Tool Development

There have been a number of verification tools for real-time systems developed during the past few years, including: KRONOS, Rt-Spin, HYTECH, CMC, Epsilon [CGL93], Polka [HRP94], TREAT [KL96], RT-Cospan [AK95], SGM [WH98], and the implementations described in [WT94]. In the following we briefly describe the tools mostly related to this thesis and compare them with our tool UPPAAL.

The verification tool KRONOS [DOY94, DOTY95, BDM<sup>+</sup>98] is originally based on the symbolic model-checking algorithm for checking TCTL-formulae of timed safety automata presented in [HNSY92, NSY92b]. The main verification algorithm in KRONOS therefore, in contrast to UPPAAL, generates the product of the analysed system before verification. It is also possible in KRONOS to check if timed automata are timed abstracting bisimilar [LY93, YT96]. Recently, the tool has also been extended with on-the-fly verification techniques to check safety properties of timed automata [BTY97].

Various algorithms to reduce the number of clock variables in a system of timed automata, without changing its behaviour, have been implemented in the separate tool OPTIKRON [DY96, Daw98]. It supports the same file format for timed automata as KRONOS, and can thus be used to improve the performance of KRONOS<sup>7</sup>.

Tripakis and Courcoubetis extends the verification tool Spin and its modelling language Promela for real-time in [TC96]. In the resulting tool, called RT-Spin, timed Büchi automata are used both as a modelling language for describing real-time system, and as a specification language for formalising requirements. Thus, its users are required to specify properties as (negated) timed Büchi automata. The verification algorithm in RT-Spin is essentially an on-the-fly, depth-first search, loop detection algorithm that checks for language emptiness of the modelled system composed in parallel with the currently checked property. The symbolic semantics of timed automata and the constraint solving techniques adopted in the tool is exactly the same as in UPPAAL.

CMC [KLL<sup>+</sup>97, LL98] is a compositional model-checking tool for networks of timed automata based on the algorithms presented in [LL95] and further developed in paper B of this thesis. Its specification language is the logic  $L_{\nu}$ [LL95, LL98] that might be seen as a fragment of the logic  $T_{\mu}$ , but more powerful than  $\mathcal{L}_s$ . Besides compositional model-checking, it is also possible to check if two timed automata are bisimilar.

HYTECH (The HYbrid TECHnology Tool) [HHWT95, HH95, HHWT97] analyses properties of systems modelled as collections of linear hybrid automata [ACHH93], a strictly more expressive model than timed automata. The tool is therefore not directly comparable with the previously mentioned tools for the model of timed automata. However, when applied to real-time system, HYTECH allows for verification of reachability properties. It is also possible to instruct HYTECH to treat certain variables in the automata as parameters and compute a condition on the parameter under which the automata satisfy a given property [HHWT95].

## 3.3 Case Studies

Naturally, all the developed tools have been tested in case studies. The number of successful applications in the literature is large and expanding, e.g. [Gri94, WT94, Abr95, HWT95, KP95, DY95, HWT96, DKRT96, CW96, MY96, DKRT97, LSW97, HSLL97, CCMM97, SMF97, TY98, BFK<sup>+</sup>98, BFM98]. It is impossible to survey them all here. We therefore restrict to case studies closely related to the work of this thesis.

In [HWT95], Ho and Wong-Toi report a case study where HYTECH is used to automatically analyse a simplified version of the Philips audio-control protocol, pre-

<sup>&</sup>lt;sup>7</sup>An extension of OPTIKRON for handling the UPPAAL file format is in work [Daw98].

viously studied without tool support in [BPV94]. The same version of the protocol was later analysed by other tools, e.g. UPPAAL (see paper C) and KRONOS [DY95]. The audio-control protocol we describe and analyse in paper E of this thesis is a more complete version of the protocol, which also includes bus-collision handling [LSW97, CW96]. It is considerably larger than the simplified version, in the sense that the number of control-nodes, components, and variables are increased.

A real-time protocol from the same application area, i.e. audio/video components, by Bang & Olufsen is analysed in [HSLL97]. Though it was known to be faulty, the error in the protocol could not be found using conventional testing methods. In the case study UPPAAL is used to produce an error-trace that reveals the error. UPPAAL is also applied to verify a suggested corrected version of the protocol, which is shown to satisfy the specified requirements.

Another industrial case study is described in [SMF97]. A control system by BMW AG which controls the height of a vehicle by regulating a pneumatic suspension system is modelled as a linear hybrid system. Correctness of the control system is formally specified as a number of safety properties and checked by symbolic reachability analysis in HYTECH.

D'Argenio et.al. presents a successful verification of a bounded retransmission file transfer protocol for lossy channels [DKRT96, DKRT97]. The protocol is based on the alternating bit protocol, but allows for a bounded number of retransmissions. To analyse all aspects of the protocol, two formal descriptions are given. An untimed, more data-oriented, version is modelled in Promela and analysed in the verification tool Spin [Hol91]. A timed version with quantified timeout values is modelled as a network of timed automata and checked to satisfy a number of safety properties, regarding the timing behaviour of the protocol, using UPPAAL.

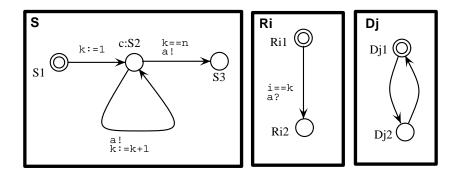

In [KLL<sup>+</sup>97], the compositional model-checking tool CMC is applied to verify the correctness of Fischer's protocol [AL92]. The mutual exclusion property of a protocol instance with 50 processes is verified using only 173 seconds<sup>8</sup> and 32 MB of memory.

Many other time-constrained systems have been modelled as networks of timed automata and specified with safety properties. Examples hereof include: the mine pump problem presented and studied in [JBW<sup>+</sup>96], the steam boiler problem proposed in [Abr95] and further studied in [KP95], the collision avoidance protocol implemented on-top of an Ethernet-like medium analysed in [JLS96, ABL98], the lip synchronisation algorithm for synchronising multiple information streams sent over a communication network, described in [BFK<sup>+</sup>98], and the multimedia stream modelled and analysed in [BFM98].

# 4 Conclusion and Future Work

In this thesis, we have developed a number of model-checking techniques for timed systems, that have been implemented in the UPPAAL tool. To evaluate the practical applicability of these techniques and impact on tool development, we have presented several case studies. In this section, we discuss the potential implication of our results

<sup>&</sup>lt;sup>8</sup>The experiment was performed on a machine running SunOS 5.5.

and lessons learnt from the work. We conclude the thesis with an outline of future work.

The main lesson learnt from our studies on verification techniques for timed systems is that relatively small restrictions on the expressive power of specification languages have rendered much more efficient verification techniques. In particular, the restriction to safety and bounded liveness properties has been of crucial importance to the efficiency of the UPPAAL model-checker. As the class of properties can be checked by reachability analysis, various optimisations on the model-checker have been focused on the on-the-fly symbolic reachability algorithm. For the compositional quotienting technique the restriction has also been important. By restricting to the safety and bounded liveness logic  $\mathcal{L}_s$  it allows the development of efficient formulae simplification strategies, which has been important to the success of the quotienting technique implemented by Francois Laroussinie in the compositional model-checker CMC [KLL<sup>+</sup>97, LL98].

The presented verification techniques and data structures have all been implemented in the UPPAAL tool except the quotienting technique. Our experiments demonstrate that they have dramatically reduced the time- and space-requirements of verification algorithms in many practical applications. However, it is important to note that they can not in general improve the worst-case complexity of verification algorithms for timed automata. It is possible to find other examples where the situation is not much improved, or where other verification techniques perform better, see e.g. [BMPY97]. It is also important to note that the reduction techniques are completely independent and can thus be combined.

Most of the examples in our case studies have been taken from the literature. We believe in that they are of general interest as they have also been studied in other contexts and verification tools. We have also presented one industrial case study which is carried out jointly with Mecel AB, a company developing control systems for modern vehicles. In this study, we developed a prototype controller for a gearbox. The case study demonstrates the potential industrial applications of the model-checking technique. In particular, it shows that the model-checking technique may be used as a powerful debugging tool in the design process of real-time embedded systems.

There are many possible future extensions of this work. We have used networks of timed automata, extended with integer data variables and arrays of such variables to formally describe real-time systems. To meet requirements from industrial applications, a more sophisticated modelling language will be needed, that supports more data types and constructs for defining abstract data types, such as lists, stacks, queues etc.

In the area of model-checking for timed systems, a main challenge is to develop techniques that combine symbolic representation of timing information with symbolic representation of control-locations. Works in this direction include [WT94, Bal96, BMPY97], however these works are either in an approximation framework or based on symbolically representing the region graph, or a discretization of the region graph.

As a concrete future work, we wish to study the control structure reduction technique presented in paper D further. One possible extension is to identify a minimal set of covering states that ensures termination and avoids repeated exploration in reachability analysis of timed systems. Recent work for finite-state systems due to Kurshan et.al. [KLM<sup>+</sup>98] gives some ideas to how a smaller set of covering states can be computed, which are applicable also in a real-time setting. Other promising related techniques for finite-state, such as the use of pseudo-root states due to Parashkevov [PY97], might also be applicable in model-checking algorithms for time-constrained systems.

# 5 Outline of the Thesis

The rest of this thesis is divided in two main parts: algorithms and data structures, and case studies.

## Algorithms and Data Structures

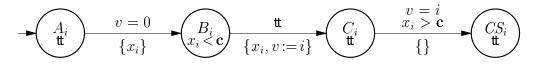

Paper A presents a process algebra of networks of timed automata and a verification algorithm based on on-the-fly and constraint solving techniques for the reachability problem associated with the algebra. As examples, an implementation of the algorithm is applied to verify a version of Fischer's protocol and a railway control system.

In paper B, these ideas are applied to develop a symbolic and on-the-fly modelchecking technique for the timed modal logic  $\mathcal{L}_s$ . The same paper also presents a compositional verification technique for  $\mathcal{L}_s$  called quotienting. Both techniques are illustrated by an example.

Paper C describes a diagnostic model-checking technique that generates diagnostic information when a certain property is (or is not) satisfied by a given network of timed automata. It is also shown how the technique was used to debug three early versions of Philips audio-control protocol.

In paper D we present two contributions to the development of memory efficient automatic verification algorithms for timed systems: compact data structure for constraints and the control structure reduction technique. An experiment were the two techniques are applied to six examples from the literature is also presented.

## Case Studies

In paper E we study Philips audio-control protocol with bus collision handing. The protocol is modelled with timed automata and analysed in UPPAAL. The same paper also describes the notion of committed locations that is used to accurately model and efficiently verify real-time systems with atomic behaviours.

Paper F presents a rigorous description of the start-up algorithm of a timed division multiple access protocol called DACAPO. The algorithm is analysed in UPPAAL and shown to satisfy its correctness criteria. An upper bound for the start-up algorithm to complete is also derived.

Finally, in paper G we describe an application of UPPAAL where the tool is applied to design and analyse a prototype gearbox controller developed at Mecel AB. It is also outlined how to check bounded response time properties in a tool like UPPAAL that only provides reachability analysis.

# References