TRITA-MMK 2002:6 ISSN 1400-1179 ISRN KTH/MMK/R--02/6-SE

# Enforcing Temporal Constraints in Embedded Control Systems

By

Kristian Sandström

Stockholm 2002

OCH KONST

KTH

Doctoral Thesis Mechatronics Laboratory Department of Machine Design Royal Institute of Technology, KTH S-100 44 Stockholm Sweden

| Mechatronics Lab<br>Department of Machine Design<br>Royal Institute of Technology<br>S-100 44 Stockholm, Sweden | TRITA-MMK 2002:6ISSN 1400-1179ISRN KTH/MMK/R—02/6—SEDocument typeDateDoctoral Thesis2002-04-19 |  |

|-----------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|--|

| <i>Author(s)</i><br>Kristian Sandström                                                                          | <i>Supervisor(s)</i><br>Christer Norström, Martin Törngren,<br>and Jan Wikander                |  |

| <i>Title</i><br>Enforcing Temporal Constraints in<br>Embedded Control Systems                                   | Sponsor(s)<br>Mälardalens University, KK-foundation                                            |  |

#### Abstract

Computer control systems are embedded in a large and growing group of products, ranging from consumer entertainment products to large airliners. Products such as automotive vehicles, aircraft, and industrial robots are equipped with advanced computer control systems and have high requirements of reliable and safe operation. A common property of these systems is that the computer systems are becoming increasingly more complex due to the inclusion of more functionality. At the same time, the product cycles are becoming shorter leading to requirements of shorter time to market. To meet this challenging task, the development of computer control systems must be a well-defined and controlled engineering process. One important part in reaching this goal is to find methods for dealing with the complexity of computer systems.

A computer control system is typically realized by a set of concurrent activities with interdependencies that have to meet a set of pre defined temporal constraints. Because of this, it is difficult to know in advance if the implementation of a design will meet its temporal constraints. Furthermore, it is hard to foresee the consequence of introducing alterations or additional functionality in a system. For a method to be useful it also has to capture all the relevant aspects of the application domain, and in the domain of embedded control systems this includes the ability to express and enforce the temporal constraints of control activities. Moreover, the computer system is a heterogeneous system with many responsibilities. Hence, methods for embedded control systems should support not only control activities but also activities related to e.g., human-machine interaction and communication.

The work presented in this thesis contributes with methods for enforcing temporal constraints in embedded control systems. The results include an industrial case study pointing out limitations in classic real-time models and giving indications of engineering needs. Moreover, a method is presented for pre-run-time scheduling of periodic control activities under the interference of sporadic interrupts. Furthermore, a method is presented for enforcement of complex temporal constraints using standard priority based real-time operating systems. Finally, the work includes a method for management of communication resources in distributed systems.

| Keywords                                                                                           | Language |

|----------------------------------------------------------------------------------------------------|----------|

| Embedded systems, real-time system, control systems, task model, scheduling, temporal constraints. | English  |

# ACKNOWLEDGEMENTS

First I would like to thank Christer Norström for an inspiring cooperation, for his dedication, and for his support. Furthermore, I would also like to thank Professor Jan Wikander, and Professor Martin Törngren for their support and for sharing their knowledge of mechatronics.

I would also like to thank the ret of my colleagues for making the daily work motivating and fun. I would especially like to thank Henrik Thane, Anders Wall, Jukka Mäki-Turja, and Roger Hassel. Moreover, I highly appreciate the review efforts made by Christer Norström, Hans Hansson, Henrik Thane, Jan Wikander, and Anders Wall.

Harriet Ekwall has provided invaluable support in all sorts of practical issues.

Finally, I am especially grateful for the strong support given by my fiancée Camilla and the daily smiles delivered by my daughter Lina.

Västerås, 5 mars 2002 Kristian Sandström

# **THESIS CONTENTS**

This thesis consists of a summary with original research papers appended. These are listed below and will be referred to in the text as papers A to D.

#### A Experiences from Introducing State-of-the-art Real-Time Techniques in the Automotive Industry

Christer Norström, Mikael Gustafsson, Kristian Sandström, Jukka Mäki-Turja, Nils-Erik Bånkestad. In Eight IEEE International Conference and Workshop on the Engineering of Computer-Based Systems, Washington, US, April 2001. IEEE Computer Society.

Kristian Sandström had part in all parts of the work presented.

#### **B** Handling Interrupts with Static Scheduling in an Automotive Vehicle Control System

Kristian Sandström, Christer Norström, Gerhard Fohler. In Proceedings of the fifth International Conferance on Real-Time Computing Systems and Applications, October 1998. IEEE Computer Society. *Kristian Sandström and Christer Norström did the main part of this work.*

#### C Managing Temporal Constraints in Control Systems

Kristian Sandström and Christer Norström. MRTC Technical Report 02/45. The work is an extension of the work presented in: Managing Complex Temporal Requirements in Real-Time Control Systems, Kristian Sandström and Christer Norström, In Proceedings of 9th IEEE Conference and Workshop on Engineering of Computer-Based Systems, Sweden, April 2002. A shorter version of this technical report has been submitted to the 8<sup>th</sup> IEEE Real-Time and Embedded Technology and Applications Symposium, California, USA, September 2002. *Kristian Sandström provided the main part of this work*.

#### D Frame Packing in Real-Time Communication

Kristian Sandström, Christer Norström, Magnus Ahlmark. In proceedings of RTCSA 2000 Korea, December 2000. IEEE Computer Society *Kristian Sandström and Christer Norström provided the main part of the work*.

# **THESIS SUMMARY**

# Contents

| 1 | Introduction                                   | 11  |

|---|------------------------------------------------|-----|

| 2 | Background and Motivation                      | 11  |

|   | 2.1 Temporal Constraints                       |     |

|   | 2.2 Temporal analysis and attribute assignment |     |

|   | 2.3 The Context of Embedded Control Systems    | 14  |

| 3 | Focus and Aim                                  | 16  |

| 4 |                                                |     |

|   | 4.1 Academic results                           | 16  |

|   | 4.1.1 Paper A                                  | 17  |

|   | 4.1.2 Paper B                                  | 17  |

|   | 4.1.3 Paper C                                  | 17  |

|   | 4.1.4 Paper D                                  | 18  |

|   | 4.1.5 Tools                                    | 19  |

|   | 4.2 Educational results                        | 19  |

|   | 4.3 Industrial relevance                       | 19  |

|   | 4.3.1 Technology transfers                     | _20 |

|   | 4.3.2 Prototypes                               | 20  |

| 5 | Conclusion and future work                     | 20  |

| 6 |                                                | 21  |

## 1 Introduction

The trend today and in the foreseeable future is the addition of more and increasingly complex functionality in embedded systems. In the development of Embedded Control Systems (ECS) a bulk of the total development time is spent on testing and maintenance. To successfully meet the challenge of developing more advanced products without increasing costs, the development of embedded control systems must put more emphasis on analysis and design. Although there are many methods for analysis and modelling of ECS described in the real-time research literature, few of them are actually used in industry. The reasons for this are manifold. The needs of industrial development processes are rarely covered by a single existing real-time method and integration of different methods can be complicated and may involve unsolved research problems. Also, some realtime methods need supporting tools in order to be useful in industry. Moreover, in developing these tools additional research problems are likely to be encountered when methods are deployed in industrial development processes. Finally, education is needed for engineers to be able to use the methods properly and efficiently.

The work provided in this thesis covers methods for use in the design and implementation of ECS. The focus is primarily on the specification, analysis, and realization of temporal constraints. The results are viewed with respect to both industrial and academic relevance.

The structure of this summary is as follows: Section 2 presents the background and motivation for this work. Section 3 presents the academic results and the industrial relevance and Section 4 provides a summary and gives directions for future work.

It should be noted that there is no overview of related work in this summary. Related work is presented in the papers that this thesis consists of.

## 2 Background and Motivation

The main goal for the work throughout this thesis has been to provide methods that aid the engineer in specifying and fulfilling the intended system behaviour for ECS. In this section, the author's view is given of what the requirements are for successful specification and verification of ECS. This section is divided into three sub sections; *Temporal constraints* describing constraints for ECS, *Temporal analysis and attribute assignment* treating the process of realising a desired behaviour, and *The Context of ECS* discussing the context in which methods for ECS should be valid.

#### 2.1 Temporal Constraints

The development process for embedded control systems is similar to that of other computer based systems with respect to the high-level process elements of design, implementation, and verification. In detail there are differences adhering to the enforcement of temporal requirements of control systems. During the design of the computer control system the activities that will carry out the intended system behaviour are formed, as are the interactions between activities and the temporal constraints of these activities and interactions. If a system is going to be formally analysed a precise model for specifying temporal constraints is required. Common in many analysis models in real-time theory is the ability to specify deadlines and/or offsets for the execution of periodical activities. Although these mechanisms are appropriate for expressing constraints on many activities, some limitations arise when used for temporal constraints related to control design. In an industrial project in the automotive industry in which the author participated, the main objective was to make an automated tool for pre-run-time scheduling. During this project the observation was made that the classical task model used was the reason for why the tool did not relieve the engineer of the scheduling burden to the extent that was intended. The engineers had to express temporal constraints originating from control system design, and those constraints were quite hard to express using the basic deadlines and offsets that were provided. When using the classical model for expressing control constraints the engineers had to manually distribute offsets and deadlines over time to make the specified system schedulable. To understand why this was necessary, one should take a look at typical control constraints and their sources.

A key property of a control system implemented on a single CPU is that only one activity can be performed at any instant in time. Moreover, the processor architecture and the software implementation result in activities that have different execution time from one activation to another. The consequences of this include:

- That activities do not have strict periodicity due to interference from other activities.

- That time varying delays are introduced between the sampling of process data and the corresponding actuation of corrective data.

- That correlated sampling activities do not necessarily observe the process at the same point in time, if executed on the same CPU they cannot execute truly in parallel.

The consequences listed above can all be dealt with by control theory and design, but will put some constraints on the real-time system models and methods. The deviation from strict periodicity for example, can be accounted for in control design if the variations have known bounds. This will in turn put requirements on the expressiveness of the used real-time models. Constraints that come from control design include:

• Constraints on the variation of the period time of execution of activities (jitter). Deviation from exact periodic execution will affect, e.g., sampling. Since exact periodic execution is hard to accommodate (in computer systems) for a set of tasks with different

period times, the ability to specify bounds for the variation is important.

- Constraints on maximum time from start of one activity to completion of another. The ability to specify bounds on the delay of control loops. In complex control systems, several control loops may interact and the period times for the different control loops might differ. This includes the ability to specify bounds on transactions where the tasks involved have different period times.

- Correlation constraints bounding the time between the executions of several concurrent activities. This type of constraint represents the behaviour of several concurrent activities that need to be synchronised in time, e.g., sampling of interrelated data. This constraint can be important in order to get a coherent picture of the state of the controlled process.

- Combinations of constraints, such as those listed above. In a control loop the variation of the period time of sampling and actuation may need to be bounded, at the same time as the time from sampling to actuation has a time limit. Furthermore, the entire control loop may be part of a larger control structure and needs to be synchronised with other activities.

The constraints listed above are relative temporal constraints as opposed to deadline and offset constraints that for periodic activities generally are absolute. As an example, a jitter constraint could be expressed using a deadline and an offset, but there exist many different deadline offset combinations that fulfil one specific jitter constraint. In a system with many activities there could be an immense number of possible combinations for assigning deadlines and offsets, and it is hard to find a solution by hand if only a part of those combinations lead to a system that is schedulable. Hence, it can be difficult to transfer control constraints to a classic real-time model with deadlines and offsets. To aid the engineer developing control systems, methods and tools based on control constraints are needed.

#### 2.2 Temporal analysis and attribute assignment

Disregarding the model used, activities specified during the design usually are implemented utilising some infrastructure, e.g., a real-time operating system and communication subsystems. To transfer information about the design to the implementation, the design information eventually has to be expressed using the infrastructure primitives, e.g., task and task attributes such as priorities. One method for assigning implementation primitives so that temporal constraints specified in the design phase are met is to make ad hoc assignments of the task attributes (e.g. priorities). The resulting system behaviour is then verified and changes in the attribute assignments are made iteratively until a satisfactory behaviour is achieved. In the design phase the verification can be done by real-time analysis methods and in later phases by testing. One problem with the manual assignment of task attributes is that it does not scale well, i.e., it is difficult to use for other than very small systems. Depending on the used run-time system, a number of more methodical approaches are available for making the attribute assignment. For pre run-time scheduled systems the synthesis is an integrated part of the scheduling phase where the execution windows of activities are constructed so that temporal constraints are met. For preemptive priority based run-time scheduled systems, methods like rate monotonic and deadline monotonic can be used to assist the engineer in assigning priorities of activities. However, as discussed earlier, ad hoc transformation of more complex temporal constraints to e.g., deadlines and offsets are not always practical. Therefore, methods are needed that either makes those transformations or make the synthesis directly from the complex temporal constraints. There exist few methods for making the synthesis from complex control constraints. Available methods for pre-runtime scheduling, e.g., [1][2][3], support control constraints but lack support for pre-emption, sporadic activities, and varying task execution times. For run-time scheduled systems there are methods with support for a sub set of the control constraints in section 2.1, e.g., [4][5].

Analysis of the temporal behaviour can both be used as part of methods for assigning task attributes and as a stand-alone tool. Besides conventional analysis methods for real-time systems based on a worst-case scenario, methods that could more accurately model the environment and the true behaviour of a control system would be beneficial. Since there is a cost in over estimating the resource requirements, the analysis should be as exact as possible. But, even if the analysis is exact it is not possible for most products to dimension the control system for scenarios that will occur at most a few times during the products lifetime. Instead temporal constraints could be guaranteed with some reliability and confidence. Potential methods could be based on quality of service for real-time systems and statistical measures for analysis. Furthermore, since the correct behaviour of an ECS is dependent on correct functional behaviour at the right point in time, methods for co-analysis of the temporal and the functional behaviour could add confidence in early analysis of a system. Potential methods include formal methods with models for representing system functionality and environmental behaviour as well as state machine based methods with support for temporal analysis.

#### 2.3 The Context of Embedded Control Systems

To make methods for synthesis and analysis of control constraints useful to an engineer there are additional constraints that must be considered to make the methods applicable in real systems. The computer system in complex embedded control systems have to cater for a vide variety of services. This includes, human-machine interaction and interfacing with communication sub systems and other target specific hardware. The control system does not only have to share the same resources with other services. It also has to interact and exchange information with them. Hence, accounting for the behaviour of other computer activities has to be an integrated part of methods for temporal analysis of computer control systems. This fact leads to a number of issues to consider when developing methods for analysing and enforcing temporal constraints of embedded control systems:

- It is important to consider both periodic and sporadic activities in the same system. Periodic activities originate in e.g., control functionality whereas sporadic activities can reflect an event-triggered behaviour or interrupt generated from e.g., the communication sub system. Both of these types of activities will coexist in most control systems. However, these two types of activities are often treated differently and separately in real-time analysis.

- The architecture of contemporary CPU's and computers, as well as the algorithms in the software implementation, lead to execution times of activities that vary from one activation to another. This directly affects the real-time analysis since e.g., jitter will be a result of a varying execution time.

- Activities in computer control system interact and have shared resources. The consequence is that methods should include mechanisms for synchronisation of the execution of activities, also between activities with different period times. Furthermore, there should be mechanisms for managing shared resources, also between periodic and sporadic activities.

Many embedded control systems are distributed systems with temporal constraints involving activities executing on different nodes and communication over a communication bus. Methods for analysis and synthesis can cover the complete system or the system can be divided into sub parts that are treated separately. If the system is treated in parts, the temporal constraints spanning several nodes must be partitioned into separate constraints for each node and bus. Two reasons for dividing the analysis and synthesis into sub parts are reduction of complexity and separate handling of system parts by sub contractors. For systems where the complexity can be managed and it is possible for one actor to control the details of the entire system it is possible to make analysis and synthesis that cover the entire system at once. For this, many methods for scheduling activities on a processor can, with modifications, be applied in planning resource usage on communication busses. However, there are additional matters to consider. In embedded control systems most data (signals) sent between activities are quite small in terms of bits and to handle them individually in bus communication would cause a large overhead. Therefore, several signals are allocated to a larger container, a frame. However, the transmission of the frame still has to meet the most severe temporal constraint of the contained signals. There are several criteria that could be considered when allocating signals to frames, e.g., resulting use of bandwidth and resulting number of frames sent to a specific node. To manage the resource usage of the bus alone is a hard task in complex systems. It could prove very hard to succeed with global system resource management, without trying to limit the complexity.

In the development of embedded control systems it is important that engineers have access to methods and tools that support the hard and complicated task of designing and implementing cooperative activities with complex temporal constraints. It is also important that the methods incorporate knowledge from both control engineering and computer engineering, in order to be a successful aid in design of embedded computer control systems. Furthermore, methods should manage real world characteristics originating from e.g., the heterogeneous nature of embedded control systems.

### 3 Focus and Aim

The main goal of this thesis is to provide methods and knowledge that assist the engineer in the design and implementation of embedded control systems. In more detail, the methods should give engineers support for describing the desired temporal behaviour of activities in a computer control system. More over, the methods should assist the engineer in transferring the described temporal behaviour to an implementation and to verify that the implementation meets the specified behaviour. The methods should also add ease to the management of temporal constraints in the process of maintenance and further development of control systems. Finally, it is important that the heterogeneous nature of embedded control systems is reflected in the methods by providing support for periodic control activities in a computer system consisting of a variety of activities such as humanmachine interaction and networking.

## 4 **Results and Contributions**

In this section the results of the thesis is organised according to academic results, educational results, and the industrial relevance of the results.

#### 4.1 Academic results

A key paper in the thesis is paper A, which treats the experiences from a project within the automotive industry. From the work presented in this paper several problems were identified and solved, mainly in paper B: *Handling Interrupts with Static Scheduling in an Automotive Vehicle Control System* and paper C: *Managing Complex Temporal Requirements - A Method for Assigning Priorities and Offsets in Fixed Priority Systems.* The work provided in Paper B presents a method for fulfilling temporal constraints in heterogeneous embedded systems by integrating handling of sporadic activities with pre-run-time scheduled periodic tasks. Paper C presents a method with stronger support for control functionality by management of complex temporal constraints for use with standard priority based real-time operating systems. Furthermore, in paper B problems

related to the implementation of the communication system is dealt with, whereas paper D proposes a method for managing communication resources in distributed systems.

4.1.1 Paper A: Experiences from Introducing State-of-the-art Real-Time Techniques in the Automotive Industry

This paper discusses some findings and conclusions from introducing real-time techniques in the development of computer control systems for automotive vehicles.

Some of the most important findings can be summarised as:

- 1. Introduction of solid real-time theory provides valuable benefits, including early error detection and less verification efforts.

- 2. Real-time theory should be transferred in the form of tools, methods, and education.

- 3. Real-time theory has poor support for some control induced temporal constraints.

- 4. Results from real-time theory has to be adapted to be useful in an industrial context, the adaptation includes research issues such as providing useful information to the engineer when the system is not schedulable.

# 4.1.2 Paper B: Handling Interrupts with Static Scheduling in an Automotive Vehicle Control System

This paper proposes a method for handling sporadic interrupts that preempts pre-run-time scheduled tasks. The motivation for this work came from introducing a pre-run-time scheduler in the development of control systems for automotive vehicles. In the system the interrupt load caused by the communication sub system was high and could not be handled by the pre-run-time scheduled system by simple ad hoc methods. The problem was solved by developing a method that accounts for interrupts in the pre-runtime scheduling process. The technique uses results for analysis of fixed priority tasks by incorporating the analysis into a heuristic tree search algorithm for pre-run-time scheduling.

This work contributes with an efficient and safe method to account for sporadic interrupts when creating a pre-run-time schedule. Furthermore, the method will add no additional run-time overhead.

#### 4.1.3 Paper C: Managing Complex Temporal Requirements - A Method for Assigning Priorities and Offsets in Fixed Priority Systems

The paper presents a method for assigning task attributes with the objective to meet complex temporal constraints for applications running on a standard real-time operating system. Using this method, complex temporal

constraints originating from control design can be expressed with a precise syntax and semantics. Based on specifications of the temporal constraints, task offsets and priorities are derived so that the constraints are met.

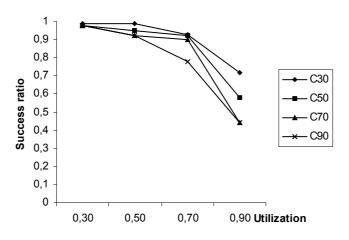

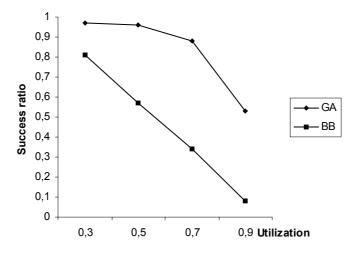

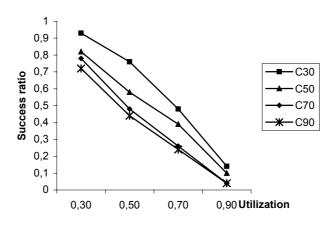

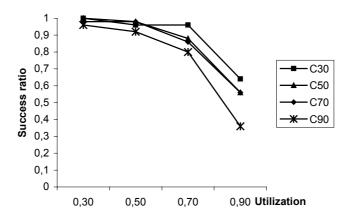

The constraints that can be expressed include; correlation constraints between concurrent sampling tasks (or actuation tasks), jitter constraints on period times, and latency constraints from sampling to actuation. Furthermore, except for periodic tasks, sporadic tasks can be specified as well as shared resources between sporadic and periodic tasks. The model also handles varying execution times of tasks. The method uses genetic algorithms to search for an optimal assignment of priorities and offsets for a task set. Simulations indicate the appropriateness of the method and the effectiveness compared to related work.

This work contributes with a strict syntax and semantics for specification of complex temporal constraints for control systems and a method for enforcement of complex temporal constraints using standard priority based real-time operating systems. Compared to methods proposed in [4][5] the method in presented in this paper can handle a larger set of constraints, e.g., both jitter and correlation constraints. Moreover methods in [1][2][3] do not handle sporadic tasks, shared resources between periodic and sporadic tasks, and varying execution times of tasks.

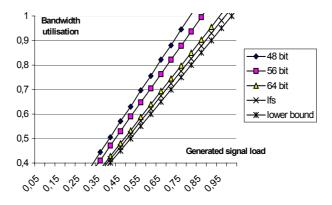

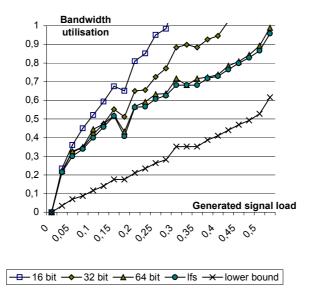

#### 4.1.4 Paper D: Frame Packing in Real-Time Communication

This paper describes a method for allocating data shared by activities over a network into frames handled by the communication subsystem. In embedded systems the size of most data sent between activities on different nodes are quite small compared to the available data containers, i.e., frames, for the bus. Even if there are small frames available the transmission overhead increases as the size of the frame decreases. As a result, signals from several activities have to be allocated to the same frame in order to reach an acceptable performance of the communication subsystem. The signals have different temporal constraints and the allocation will therefore affect the bus utilisation. In fact, finding frame sizes and making proper allocation of signals to frames so that the bus utilisation is minimised is a NP-hard problem. The method presented allows fast allocation of very large signal sets with good result with respect to bus bandwidth utilisation. The method is based on approximation algorithms and simulations are used to verify the appropriateness of the algorithms.

The work presented in this paper makes contributions by formulating the packing problem, showing that the packing problem is NP-hard, presenting a simple and effective heuristic for frame packing, and demonstrating the effectiveness of the algorithm on realistically sized problems derived from the automotive industry.

#### 4.1.5 Tools

To aid the development and evaluation of methods for managing temporal constraints in ECS two software tools have been developed.

*GenECS* is a tool for generating simulated system specifications for embedded control systems. The tool generates task sets with temporal constraints according to a predefined profile. It is possible to control the distribution of values generated for attributes such as the worst and best case execution times, deadlines, jitter constraints for period times, and utilisation for sporadic and periodic tasks.

*TemporalControl* is a tool for assigning attributes for pre-emptive priority based real-time operating systems. Given a specification of a task set with temporal constraints the tool assigns priorities and offsets to the tasks so that the constraints will be met during run-time. The task set can include both periodic and sporadic tasks with synchronisation constraints and shared resources. Temporal constraints that can be solved include jitter, correlation, and latency.

An earlier version of the tools where developed as part of a master thesis conducted by Johnnie Blom under supervision of Kristian Sandström.

#### 4.2 Educational results

The knowledge gained during the work of the thesis has been exploited for many educational purposes. As the most prominent the following are mentioned:

- The development of course material and lab exercises for a basic course in real-time systems at Mälardalen University.

- Development and realisation of several instances of a large-scale project course in distributed real-time systems. Research results have been applied in the course, e.g., in a project developing design and analysis tools for embedded real-time systems.

- A compendium in real-time systems used at Mälardalen University, Uppsala University, and Dalarna University.

#### 4.3 Industrial relevance

Throughout the work of this thesis there have been an exchange of knowledge with industrial partners. Methods have been tested in industrial cases and research issues have been extracted from problems found in industrial projects. Furthermore, several courses in real-time systems have been given to industry. In the rest of this section, the more extensive co-operations are presented.

#### 4.3.1 Technology transfers

In a project with Volvo Construction Equipment Components a real-time design model and analysis was introduced in the development of their computer control system. The model has evolved and is still in use in the development of the embedded control system for construction equipment. From this project a lot of problems were identified, and some of them are solved in this thesis.

In a master thesis [6], methods for allocation of signals to frames and scheduling of frames on the network where developed. The work was conducted in cooperation with Volcano Communication Technologies. A simulation environment was developed and the results have later been used in an industrial project.

#### 4.3.2 Prototypes

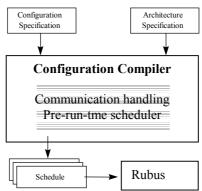

As a commercial spin-off, a prototype tool for pre run-time scheduling, the Configuration Compiler, was developed. The prototype was developed for use at Volvo Construction Equipment Components and is now incorporated in the tool set for the commercial real-time operating system Rubus provided by Arcticus Systems.

## 5 Conclusion and future work

In order to develop and maintain embedded control systems of higher quality in shorter time, it is important that methods and tools support the complex task of computer control system development. Tools and methods that help the engineer to formulate and enforce the complex temporal constraints put on control systems are needed. Furthermore, since most embedded control systems are heterogeneous, support for systems consisting of subsystems with different characteristics are required.

This thesis proposes methods for specification, analysis, and synthesis of temporal constraints for embedded control systems. Furthermore, methods are provided that are adapted for the reality of embedded systems with a mix of control and computer system related functionality. The contributions are:

- An industrial case study pointing out limitations in classic real-time models and giving indications of engineering needs.

- A strict syntax and semantics for specification of complex temporal constraints for control systems.

- Scheduling off periodic control activities under the interference of interrupts.

- A method for enforcement of complex temporal constraints using standard priority based real-time operating systems.

- A method for management of communication resources in distributed systems.

Several tools and prototypes have been developed to validate the results and some of the prototypes have been transferred to industry and are in successful use today.

In future work the author would like to investigate how the methods can be better adapted to practical operating conditions of a system. The method for attribute assignment presented in this thesis assigns attributes based on a safe analysis using a system model that will represent the outer boundaries, with respect to the temporal behaviour of the real system. The analysis will often provide over estimations if compared to how the real system will behave. The main part of this pessimism in the analysis comes from the assumption that sporadic activities will be activated with their maximum frequency and with a worst-case phasing relative the periodic activities. In the real system, this is in many cases unlikely to occur and surely in some cases it cannot. For many products housing embedded control systems, the price of having absolute certainty, with respect to resource usage, cannot be justified. Instead the system could be dimensioned to meet its temporal constraints with some probability within some confidence interval. One possible method for achieving this property for the method presented in paper C would be to base the analysis part of the genetic algorithm on samples taken from simulations.

Another possible direction for future research is to look at methods for use earlier in the development process and how they link to the methods presented in this thesis. Since, an undetected error made in early development is much more expensive than an error made late it is important to have early measures of the possibility to meet functional and temporal constraints. It is also important to find a coherent methodology that connects methods throughout the development process from architectural analysis to implementation and maintenance.

## 6 References

- [1] Mok A. K., Tsou D., and De Rooij R. C. M. The MSP.RTL Real-Time Scheduler Synthesis Tool. In Proc. 17<sup>th</sup> IEEE Real-Time Systems Symposium, pp. 118-128. IEEE Computer Society.

- [2] Würtz J. and Schild K. Scheduling of Time-Triggered Real-Time Systems, In Constraints, pp. 335-357, October, 2000. Kluwer Academic Publishers.

- [3] Cheng S. T. and Agrawala A. K. Allocation and Scheduling of Real-Time Periodic Tasks with Relative Timing Constraints. Second International Workshop on Real-Time Computing Systems and Applications (RTCSA'95) October 25-27, 1995.

- [4] Bate I. and Burns A. An Approach to Task Attribute Assignment for Uniprocessor Systems. In Proc. 11th Euromicro Conference on Real-Time Systems (ECRTS99), York, England, June 9-11, 1999, IEEE Computer Society.

- [5] Gerber R., Saksena M, and Hong S. Guaranteeing Real-Time Requirements with Resource-Based Calibration of Periodic Processes. IEEE Transactions on Software Engineering, 21(7), July 1995.

- [6] Ahlmark M. Local Interconnect Network (LIN) Packaging and Scheduling. Master Thesis, Department of Computer Engineering, Mälardalens University, June 2000.

# **PUBLICATIONS**

# Managing Complex Temporal Requirements in Real-Time Control Systems

Kristian Sandström and Christer Norström. In proceedings of 9th IEEE Conference on Engineering of Computer-Based Systems, Sweden, April 2002.

# **Experiences from Introducing State-of-the-art Real-Time Techniques in the Automotive Industry**

Christer Norström, Mikael Gustafsson, Kristian Sandström, Jukka Mäki-Turja, Nils-Erik Bånkestad. In Eigth IEEE International Conference and Workshop on the Engineering of Compute-Based Systems Washington, US, April 2001. IEEE Computer Society.

#### Verifying Temporal Constraints on Data in Multi-Rate Transactions

Anders Wall, Kristian Sandström, Jukka Mäki-Turja, Christer Norström. In proceedings of RTCSA 2000 Korea, December 2000. IEEE Computer Society.

#### Frame Packing in Real-Time Communication

Kristian Sandström, Christer Norström, Magnus Ahlmark. In proceedings of RTCSA 2000 Korea, December 2000. IEEE Computer Society.

# Findings from introducing state-of-the-art real-time techniques in vehicle industry

Christer Norström, Mikael Gustaffson, Kristian Sandström, Jukka Mäki-Turja, Nils-Erik Bånkestad. In industrial session of the 12th Euromicro Conference on Real-Time Systems, Stockholm, Sweden, June 2000.

#### Modeling and Scheduling of Control Systems

Kristian Sandström. Licentiate Thesis, ISSN 1400-11791, Department of Machine Elements, The Royal Institute of Technology, Sweden, 1999.

#### **Constructive Feedback turns Failure into Success for Pre-Scheduled Systems**

Kristian Sandström, Christer Norström. In Swedish National Real-Time Conference SNART'99, August 1999.

#### **Towards Efficient Analysis of Interrupts in Real-Time Systems**

Jukka Mäki-Turja, Gerhard Fohler, Kristian Sandström. In work in progress, 11th EUROMICRO Conference on Real-Time Systems, York, England, May 1999.

#### Handling Interrupts with Static Scheduling in an Automotive Vehicle Control System

Kristian Sandström, Christer Norström, Gerhard Fohler. In Proceedings of the fifth International Conferance on Real-Time Computing Systems and Applications, pages 158-165, October 1998. IEEE Computer Society.

#### An Overview of RTT: A Design Framework for Real-Time Systems

Christer Norström, Jukka Mäki-Turja, Kjell Post, Mikael Gustaffson, Jan Gustafsson, Kristian Sandström, Ellus Brorson. Journal of Parallel and Distributed Computing, no 36, August 1996.

#### A Graphical Design Environment for Development of Object-Oriented Hard Real-Time Systems

Christer Eriksson, Roger Hassel, Lennart Myrehed, and Kristian Sandström. TOOLS Europé 95, Paris, France, Mars 1995. Published in TOOLS 16 by Prentice Hall, ISBN 0-13-443128-6.

A

# Experiences from Introducing State-of-the-art Real-Time Techniques in the Automotive Industry

by

Christer Norström, Mikael Gustafsson\*, Kristian Sandström, Jukka Mäki-Turja, and Nils-Erik Bånkestad\*\*

Mälardalen Real-Time Research Centre, Department of Computer Engineering, Mälardalen University, Västerås, Sweden \*TietoEnator ArosTech AB, Västerås, Sweden \*\* Volvo Construction Equipment Components AB, Eskilstuna, Sweden

In Eigh IEEE International Conference and Workshop on the Engineering of Compute-Based Systems, Washington, USA, April 2001. IEEE Computer Society.

## Experiences from Introducing State-of-the-art Real-Time Techniques in the Automotive Industry

Christer Norström, Mikael Gustafsson, Kristian Sandström, Jukka Mäki-Turja, and Nils-Erik Bånkestad

Mälardalen Real-Time Research Centre, Department of Computer Engineering, Mälardalen University, Västerås, Sweden \*TietoEnator ArosTech AB, Västerås, Sweden \*\* Volvo Construction Equipment Components AB, Eskilstuna, Sweden

#### Abstract

The use of state-of-the-art real-time techniques in industry is still rare. The reason for this is three-folded: (1) the lack of commercially available tools, (2) the lack of methodologies that considers real-time throughout the complete development process, and (3) the lack of competence in real-time theory among industrial practitioners.

In this paper we present a case study of introducing state-of-the-art realtime techniques in industry. The case study was done as a collaboration between Mälardalen University and the industrial partners Volvo Construction Equipment AB (VCE) and TietoEnator ArosTech. VCE develops computer control systems for construction equipment vehicles, such as wheel loaders, graders, and articulated haulers. TietoEnator ArosTech is a firm of consultants with expertise competence in the area of embedded real-time systems.

We will present both the used methodology and the findings from introducing this methodology in an industrial project. The methodology emphasis is on introducing timing requirements early in the design of a system and it relies on the use of a well defined design language. We will present our findings categorized into methodological aspects, technology transfer, and technical aspects. The main result reported can be summarized as "people, not paper, transfer technology".

#### **1** Introduction

Development of complex embedded systems is a growing area, i.e., we see more and more applications that are dependent on the use of embedded computers. Examples include highly complex systems, such as medical control equipment, mobile phones, and vehicle control systems.

Most of the embedded systems can also be characterised as real-time systems, which means that their correct function is dependent on both correct functional results and that the results are produced at the correct time.

The increased complexity of these systems leads to increasing demands on issues such as requirements engineering, high level design, early error detection, productivity, integration, verification, and maintenance. This calls for methods and models that enable a controlled and structured way of working during the complete life cycle of the system [Kal88].

There exist many design methods for real-time systems like, UML-RT and HRT-HOOD. However, these methods often concentrate on the logical and structural decomposition rather than focusing on the temporal behaviour. The temporal behaviour is often added on top. This is not so strange since these methods are based on general software development methods that are not focusing on embedded real-time systems. Furthermore, these methods have no, or limited, support for high level timing analysis and do not provide support for automatic mapping from the design to a resource structure. This often leads to a semantic gap between the design and the implementation, that is, the code and design description may not describe the same version of the system. Thus, classic problems during integration may occur, such as erroneous synchronisation and communication interfaces and that the system is hard to maintain.

Therefore, we have developed a model and method focused on the realtime properties of a system. The key property of the model and method is specification of a high level design that includes the specification of temporal constraints, communication and synchronisation. Furthermore, the model and method supports formal verification of these properties, early system integration, and efficient testing.

The aim of this paper is to briefly present this model and method, as well as our findings from introducing and using them in an industrial project. This project was performed as a cooperation between Mälardalen University, Volvo Construction Equipment AB (VCE) and TietoEnator ArosTech.

VCE has had onboard electronics since 1981 for specific functionality. Currently more and more functionality is provided by the computer control system. This has led to an increased number of people involved in the development of each product, and thus the need for better development methods and tools.

This was the motivation for the university to participate in the development of a new computer control system for the next generation wheel loaders. Since a complete new architecture was to be developed we were given the opportunity to introduce new technologies and methods.

Many functions are similar in different vehicles and therefore it would be a desired property to be able to reuse existing solutions. This was the starting point for defining a new architecture that could be used for all types of future construction equipment. Hence, the result of this project will act as a basis for extracting a product line architecture [Bos00]. However, the latter step is outside the scope of this paper.

Thus, this paper is focused on presenting our findings from introducing state of the art real-time technology in an industrial project. The validity of these findings is based on a single, but extensive, case study of one industrial project. Some of the findings are strengthened by similar results in other industrial projects that also have utilized state of the art real-time technology [Cas98, Mel98].

The outline of the paper is as follows: Section 2 presents briefly the characterization of the application. The design language used is described in Section 3. Section 4 presents briefly the tool that maps the design to a resource structure. Thereafter, in Section 5, the development methodology is presented. In Section 6 we present our findings categorized into findings related to methodological aspects, technology transfer, and technical aspects. Finally, in Section 7 some conclusions are given.

## 2 Application characteristics

The application is a vehicle control system with high demands on safety, reliability, and timeliness. The hardware in the system consists of two nodes that are connected via redundant buses. The application contains tasks, running at different period times, which collaborate to perform certain control functions. The system contains about 80 tasks with well-defined functionality. Each node is very I/O intensive. The complete system has about 150 I/O channels connected to it.

The execution times of the tasks in the application range from about 10  $\mu$ s to 1 millisecond. The application is, due to the construction of the hardware, interrupt intensive. Since this application has many interrupts, the effect of these interrupts cannot be neglected when scheduling the application tasks.

The worst-case utilization of the processors for the critical part is around 80%, divided into 35% for interrupts and 45% for application tasks. The spare capacity left is used by soft real-time tasks. At run-time, the spare capacity will be more than the remaining 20% if the load is less than the worst case.

The reason for the extensive use of interrupts is mainly due to the hardware design. The hardware could not be modified since it was already designed and certified when the software development started.

#### 3 Design language

The design language should be simple with a few, but powerful, constructs with clearly defined syntax and semantics. The reason for this is twofold: 1) parts of the implementation can be automatically generated by tools and, 2) the traceability from specification to implementation is improved since it is easier to overcome the semantic gap between design

specification and implementation. The design is tightly coupled to the implementation; it is easier to fix a bug by correcting the design than to just make a modification in the code, when tools generate parts of the implementation directly from the design specification.

Another important principle is the separation of concerns. A specific example in the language is to separate communication and synchronization constructs from the C-code. This gives advantages in verifying the temporal behavior of the system (analyzing or estimating the execution time of the code is easier since it is independent from other components of the system). The integration phase also becomes easier when the interaction and synchronization is specified and analyzed early in the design.

The most important contribution, however, is that temporal constraints are defined early in the development process, which enables an early temporal verification.

The key elements of the language in increasing order of granularity are:

- Application defines the top level of a complete software system.

- Modes and mode transitions defines a high level state machine.

- Transactions describes the functionality in a mode.

- Interaction graphs describes the interactions between tasks that make up a transaction.

- Tasks the computational elements of the design language.

#### 3.1 Application model

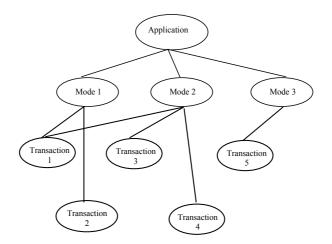

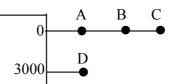

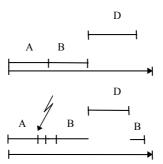

A classical way of attacking problems is by "divide and conquer", i.e., by decomposing the problem into more manageable sub-problems. This is done here by hierarchical decomposition, where an application is broken down into modes. A mode is an operational state of the application. Different modes contain different functionality. Each mode should only include the functionality that is needed for the desired behaviour. A picture of this hierarchy is shown in Figure 1.

**Figure 1: Application model**

#### 3.2 Modes and mode transitions

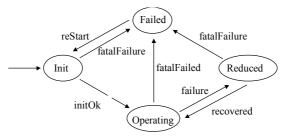

A mode describes specific functionality in a system state. If the functionality differs substantially from one state to another, one should separate them into two different modes. An example is the control system in a vehicle, which can have different functionality depending on the status of the vehicle. If the vehicle is fully functional, the control system is in full operating mode. If a severe error occurs the control system can take the vehicle into a reduced functionality, mode where only the most critical functions of the control system are provided, so that the vehicle can be taken for repair.

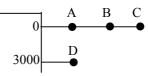

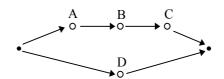

Modes in the system are described in a mode transition graph, comparable to a state transition graph, where all legal transitions between modes are depicted. An example mode transition graph for our vehicle is illustrated in Figure 2.

#### Figure 2: Mode transition graph for a control system for a vehicle

Why modes? In almost all application there is some kind of mode concept, even if implicit. For example when the system is starting up, initialisation functionality is provided which is no longer needed when the system is fully operating. Many systems also have a failure mode with reduced functionality. If there is no way of specifying these modes they have to be implemented ad hoc in the code which makes it hard to understand and maintain the system.

#### 3.3 Transactions and interaction graphs

For each mode a number of functions must be provided, we call these transactions. A transaction consists of a collection of tasks that together provide the desired functionality. The interaction and dependencies between tasks are described by communication and synchronisation constructs. Communication is specified as a directed relation from one task to another. Synchronisation can be described by precedence relationships between tasks or by mutual exclusion of task that share a common resource. The temporal behaviour of tasks in the transaction is specified by temporal attributes of single tasks. Besides tasks, interrupts can also be specified. Including interrupts in the specification makes it possible to include them in the analysis.

#### 3.4 Task

A task is the smallest executable unit. A task is described with a set of functional and temporal parameters:

#### Functional:

- Entry function. The entry function specifies the function to perform on each invocation. This, together with the state and input, defines the functionality of the task.

- State. A task has some state variables, (comparable to instance variables of an object), which keep their values across activations of the task. The variables constitute the task state.

- **Ports**. Since communication primitives are not allowed in the code, communication is specified in the interaction graph. Each task is equipped with in- and out-ports. The in-ports acts as input to the entry function and the result of the entry function is placed on the out-ports of the task.

#### Temporal:

- **Period time**. The period time of the task.

- WCET. Worst Case Execution Time of the entry function. Note that this value is assessed and used as an additional design parameter during the design and verified after implementation.

- **Release time**. Remember that every task is a member of a precedence graph and therefore has a period. The release time is the earliest time the task can be activated, relative to its period start.

- **Deadline**. The deadline is the latest time a task is allowed to terminate, relative to its period start.

The *execution semantics* of a task is at activation to read the in-ports, thereafter perform the function, and before termination write the result to its out-ports. This construction means that each task can be designed without

knowing where the input data was produced and where the produced output data will be used.

## 4 Mapping of the design to a resource structure

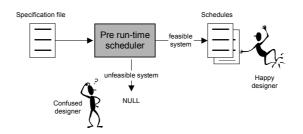

The Configuration Compiler tool maps a textual based description of the design to a resource structure, as illustrated in Figure 3. The Configuration Compiler is a pre-run-time scheduler that generates dispatch tables and communication infrastructure for each mode. Besides the mapping of the model, the tool also supports specification of architecture specific attributes like performance, the time granularity of the run-time dispatcher, communication times, and number of nested pre-emptions allowed. The implementation of the Configuration Compiler is based on a heuristic tree search strategy, similar to the one presented in [Ram90]. The major difference is that this scheduler takes interrupts and architecture specific attributes into account. The current version of the tool is adapted to the real-time operating system Rubus<sup>1</sup>.

**Figure 3: The Configuration Compiler**

# 5 Development methodology

The development methodology defines the workflow when developing an application. The methodology employed in this project is iterative and quite traditional. The emphasis in the method is to derive a high level design that enables early schedulability analysis. To facilitate this it is required that synchronization, communication, and temporal attributes are defined early in the design process, which is of no problem except for execution times of the tasks. The execution times are normally derived from the code. However, in this approach we specify (estimate) an execution time budget for each task. The execution time budget is later in the implementation phase used as an implementation requirement. Estimating the execution time budgets is a delicate issue that requires highly skilled engineers with a lot of experience. However, if the estimate can not be fulfilled a negotiation strategy has to be employed. That is, execution time may be borrowed from

<sup>&</sup>lt;sup>1</sup> Rubus and the Configuration Compiler are commercial products, see www.arcticus.se.

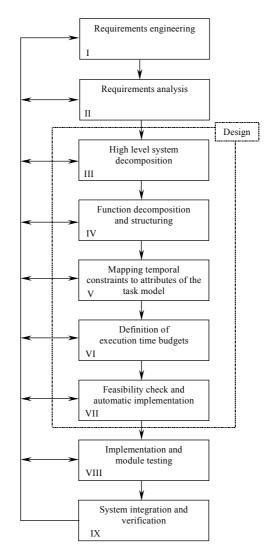

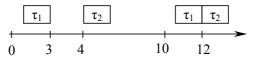

another task, which does not utilize the allocated execution time. The development methodology is general and can be adapted to different design languages (modeling languages). The method is briefly described in Figure 4 and by the following text.

- I. **Requirements engineering**. Here are the requirements formulated by the customer of the system.

- II. **Requirements analysis**. In this stage the functions of the application are identified from the requirements specification. An important aspect here is also to determine temporal constraints for these functions.

- III. **High-level system decomposition**. In this stage the application's different operational modes are identified together with valid transitions between them, by specifying the mode transition graph.

- IV. Function decomposition and structuring. The functions, for each mode, are decomposed into transactions. Note that one transaction could belong to several modes. Transactions are decomposed into smaller units called tasks and their low-level functions are specified together with the data flow information between them. Some high level functions has parts that have a high demand of responsiveness or are very frequent (but small) so that implementing them as tasks would be infeasible. Therefore such low-level functions are implemented as interrupts. This is formally described in an interaction graph.

Figure 4: The design methodology

- V. **Mapping temporal constraints to attributes of the task model**. In the previous stage the high level functions were decomposed into smaller units and structured according to the interaction between them. This step has to brake down the high level temporal requirements into temporal attributes for these smaller units. The expressiveness of the task model attributes are different, and lower level, than specified for the high level functions, so it is important that this transformation is done in a safe way, i.e., that the task model attributes does not violate any of the high level constraints. It is also important that this mapping does not overconstrain the system.

- VI. **Defining Execution Time Budget**. Traditionally the assessment of WCET is done by either measurements or by statically analyzing the code produced for each task. In this approach, however, execution time budgets are defined, these budgets are later in step VIII used as implementation requirements. The reason for this is that a feasibility test for the system, and a possible re-engineering, can be done at an

early stage, and thus provide early detection of design errors related to resource utilization, communication and synchronization.

- VII. Feasibility check and automatic implementation. The formally described design can be checked for temporal correctness even if no actual (low-level) implementation has been done. This is done by a static scheduler, which tries to find a feasible schedule. Besides the schedule, the communication infrastructure is automatically generated.

- VIII. **Implementation and module testing**. The implementation of tasks is simply done by traditional programming (coding). Besides the traditional functional specification, the programmer also has the execution time budget as an implementation requirement, i.e., the programmer has to implement the specified function in a way that it does not violate the budget. The module testing includes both verifying the functional behaviour as well as that the time budgets are not violated. If the time budget cannot be met a redesign has to be done.

- IX. **System integration and verification**. The integration phase is usually done very quickly and without problems since the actual integration was done in the design with a strict semantics. The major work is to do the integration testing.

The above figure and listing defines the activities performed in each step, and the iteration when using this method.

## 6 Findings

In this section we will describe the findings acquired when introducing and using the design language and method earlier described in Section 2. The findings are categorized into those related to development methodology, technology transfer, and technical issues respectively. The development methodology covers the findings based on the use of the design language and method. The technology transfer part describes issues regarding the transferring and introduction of new technology and especially real-time technology into an organization. The technical issue part presents new or relevant technical challenges that have been discovered during this work.

#### 6.1 Design methodology

Finding 1: The design language provides a good basis for the design description.

#### Motivation:

Using the design language described in Section 3 gives three major benefits when designing a system:

1. It gives a skeleton of the application, which can be analysed without having a single line of code.

- 2. The analysis leads to early error detection of communication, synchronization, and timing errors.

- 3. Simplified system integration.

Currently we can analyse communication, synchronization, and timing requirements. Communication is analysed in three different aspects. Firstly, the types of connected ports are checked, which ensures that the proper data types are passed to the tasks. Secondly, the analysis will reject a design where the amount and rate of data passed through the system makes it infeasible to fulfil the timing requirements. Thirdly, data consistency is checked. Again, if there is no possible way of fulfilling all timing requirements and at the same time guarantee data consistency, the design is rejected.

The analysis of the synchronization makes sure that all precedence and mutual exclusion relationships between tasks can be guaranteed in conjunction with guaranteeing the timing requirements.

Finally the analysis of the timing requirements reveals if it is possible to find a schedule for the given design and execution time budgets that fulfils these timing requirements. If it is impossible to fulfil the timing requirements the design will be rejected.

The analysis presented above leads to early detection of errors, in the design, of the properties that are analysed. Such errors are otherwise often found in the integration phase of the project and thereby cost a lot of time and effort to correct.

System integration is also simplified by the early analysis. If the implementation of the code of each task comply with the interface given by the design, i.e., retrieving data only from the in-ports, performing the desired function within the given execution time budget, and producing data only to the out-ports, then the integrated system will fulfil the design and thus satisfy the requirements. Thus, a step of the development process, that often tends to be quite troublesome and leading to costly delays in the project, are simplified.

Note that the only thing that has to be added to implement the design is the task code, everything else is automatically generated, i.e., communication, synchronization and an execution scenario (schedule).

Finding 2: The use of a precise design language

- a) Enables parallel implementation and testing of the tasks.

- b) Facilitates efficient integration of new personnel into the project.

Motivation:

a) The task model stipulates tasks, which have no synchronization or communication within the code. Recall from section 2, that each task uses a computational model based on input - calculation - output. That leads to that each task can be implemented and tested in parallel since each task is only dependent on its own state and the values of its in-ports to make a calculation. The module testing is, thus, very simple to make, just feeding values to the in-ports and monitoring the output. This also allows regression testing of modules.

b) One small group of people, who have good knowledge about the system and a good feeling of future demands on the systems, develops the design. The design they come up with must be stable, that is, not too many major changes are allowed to occur after the implementation phase start. If that is accomplished, it is easy to introduce new personnel into the implementation phase since each new employee or consultant only has to understand the design language and obey the given interface to be able to start to implement and test. The design language has decreased the introduction time for new employees substantially.

**Finding 3**: The methodology increases the time spent in the design phase but shortens the implementation time.

#### Motivation:

We feel that the time to complete the design phase has increased compared to similar projects, which have used traditional informal techniques (such as structured analysis and design). This is not surprising since a precise design with analysis is harder to come up with, compared to a design that just is based on written documents. However, we feel also that the precise design has lead to shorter time spent on implementation, test, and integration due to reasons described earlier in this section. We also believe that it will be much easier to maintain a system based on a precise design compared to a traditional system. This is mainly due to two reasons:

- 1. Normally the implementation and the design tend to diverge which makes it hard to foresee the impact of changes and added functionality. This can be avoided by the fact that the tools are useful and actually produces verified functionality. It is for example quite natural and widely accepted to use the compiler instead of adding object code here and there. Another restraining factor can be the fear of disturbing the order laid out by the tools, again compare with the compiler example.

- 2. Even if there is a good match between the design documents and the implementation it is not easy to foresee the impact of changes and added functionality. In our case several properties of the altered design can be analysed, as discussed earlier, already in the design phase. So changes or add-ons that does not comply with the implemented functionality will be detected.

**Finding 4**: Execution time budgets for tasks turned out to be good as a design tool and implementation requirement.

#### Motivation:

To be able to make an early capacity analysis of the resources in the system, like processors and buses, each task has to have an execution time

budget. This budget states how much of the processor capacity the task is allowed to utilize. The difficulty in specifying this budget is to relate the execution time budget to the functional requirements of the task, e.g., for a controller it should be possible to fulfil the desired control performance within the specified time budget. If it is not possible this time budget is erroneous. The execution time budgets are then used as implementation requirements.

In this project we were really surprised that these budget estimations where so good. However, the engineers that specified these budgets had many years of experience in control system design and good knowledge about hardware close programming.

To verify that the implementation fulfils the requirements the execution time for the tasks was measured and sometime calculated.

## 6.2 Technology transfer

**Finding 5**: To be able to transfer real-time technology to industry; tools, education (courses, tutorials), carriers, and adapters are required.

### Motivation:

Tools:

When transferring theories to the industry it is necessary that the theory is encapsulated in a tool, which shows the practical use of the theory [Sch96], unless the theory is very simple [Bat99]. A good example of a tool that encapsulates advanced technology well is a traditional compiler. In this case the tool was in the first version an application written in a high level language that was easy to adapt to up-coming requirements from the industry. To handle these up-coming requirements in an efficient way is important to succeed in the transfer, a part where the carrier described below play a significant role. The tool was later ported to a low-level language to get an efficient implementation.

### Courses:

We have found out that an engineer requires at least two days of training to understand the basic real-time theory and the added methodology to be able to work with design of new systems. So in reality for an experienced engineer it will take about one week including the training course to be productive, from the model and methodology point.

### Carrier:

The success of this transfer is mainly because one person, that worked in the research group where the ideas where developed, started to work as a consultant for TietoEnator ArosTech at VCE. Regardless how many good reports we write we need people that carries the results [Dal94]. A related example is the development of the control system for Volvo S80 where Ken Tindell and others carried the response time analysis for the CAN bus into a tool and implanted that tool into Volvo Car Cooperation organization [Cas98, Mel98].

Citation: "Tech transfer is a contact sport. People not paper transfer technology" [Fol96].

#### Adapters:

Even if we have carriers we need early adapters at the company that take the technology into the company and its organization. These people need to be authoritative to be able to sell the new technology in the organization. There is always a healthy conservatism in all organization. Therefore one must find people that are ready to invest enough time and energy to find out if the technology is applicable and gives an added value to the development of their products or not [Ben96].

**Finding 6**: The major problems when introducing real-time technology in an organization is to change the requirements caption process to include timing requirements.

#### Motivation:

Several independent sources have given the same statement (Volvo Car and Volvo Construction Equipment). Especially since all engineering disciplines within a company has to change their way of specifying requirements on the electronics. The main problem is that once a timing requirement for a high-level function has been derived, it is very hard to reconsider it later on. It seems that a timing requirement becomes more and more truthful the older the timing constraint becomes. This really comes to the surface when a new function is added and the schedulabilty test is negative depending on that the utilization of the system is too high. To add this function anyway you need to find either execution time budgets that are too generous or timing requirements that are too strict. Assuming the overestimation of execution times is neglectable, the timing requirements have to be reconsidered. To find out which timing requirements that have to be relaxed there must exist a notion of confidence of the timing requirements. As an example, the time from pressing a particular lamp switch until the light is turned on should it take 200 ms or 300 ms, if the requirements say that the confidence in specifying 200 ms is low this timing requirement could be considered to be relaxed. Thus the results from the requirements caption process must be clearly expressed and well motivated since it will be used during the complete life cycle of the system.

## 6.3 Technical issues

**Finding 7**: The task model used (described in Section 2) is in some cases too restricted when handling control jitter for simple controllers and especially for multirate controllers.

#### Motivation

The *limited expressiveness* in the used task model is related to the jitter problem and multirate communication problem. Specifying release times and deadlines of the tasks involved in the computation can be used to fulfil for example jitter requirements. However, this is a problem since the engineer has to distribute the release times and deadlines at the timeline to not overload a specific window of the timeline. This means that the engineer has to act as a pre scheduler to the scheduler, which is not efficient. Instead, a desired property of the task model would be to have the possibility to specify relative timing constraints. For example, a sampling task is required to run with a certain period time and have a tolerance of a specific amount (*Period time*  $\pm$  *tolerance*). Relative timing constraints could also be used for specifying latency constraints, e.g., the time between sampling and actuation. Furthermore, when a controller consists of several entities that run with different period times, i.e., multirate control, one would also like to have the possibility to specify latency constraints. If the used task model supported this it would be much simpler to specify a system. Extending the task model is an easy task but to come up with useful tools to schedule a system based on such a task model is not an easy task.

**Finding 8**: Task model and scheduling techniques reported in literature has to be extended to take real-world requirements into consideration.

#### Motivation:

When the scheduling tool for this task model was developed we had to take several important aspects into account to be able to get a tool that utilized the resources of the target system efficient. The two aspects we will cover here are schedule representation and taking interrupt overhead into account when constructing the same schedule.

Schedule representation. A common representation of a static schedule is a vector, where one position in the vector represents a discrete point in time at which the execution of a task can start. The granularity of time has to be matched with the frequency of the periodic clock that drives the dispatcher, which will execute the tasks according to the schedule. If the execution time of a task is less than this granularity, or if it exceeds a multiple of the granularity with a small fraction, then the utilization of the CPU resource will decrease. This because there will be time intervals that can not be used to execute tasks. An apparent solution to this is to increase the granularity (frequency) of the periodic clock. However, with a higher frequency of the clock the dispatcher will instead use more of the CPU resources, since it will execute more often.

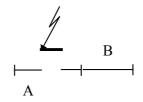

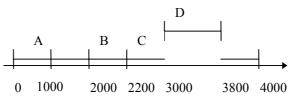

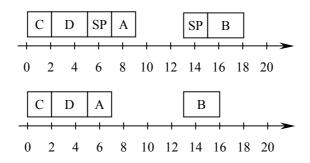

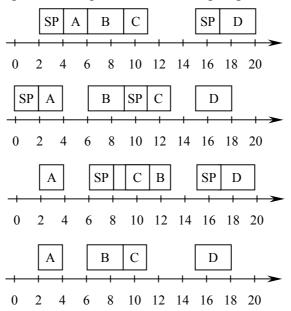

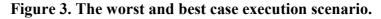

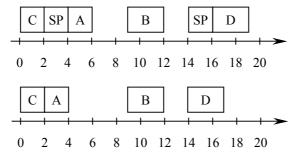

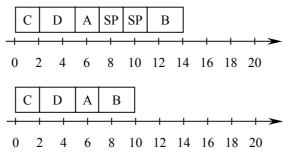

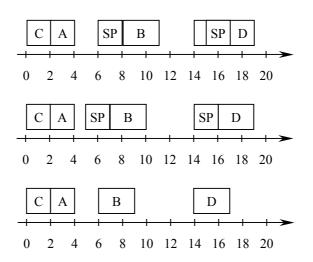

Figure 5: The representation of a schedule.

Another way of representing a schedule is as a list of rows, see Figure 5, where each row represents a point in time at which the dispatcher is to start the execution of a sequence of one or more tasks. The first task in this sequence, or *chain*, is started at the given point in time. All other tasks in the chain are started as soon as the preceding task in the sequence has completed its execution, without need for the clock to trigger the dispatcher. This representation will allow several tasks to be executed during an interval less than the period time of the dispatcher clock. Hence, the dispatcher overhead can be kept low at the same time, as the utilization of the CPU resource is high.

**Interrupt overhead.** Typically, pre-run-time scheduling does not account for interrupts, assuming their execution can be ignored or incorporated into task execution times. In many applications, the interrupts are, however, non-negligible and inclusion in task execution is too pessimistic and inefficient. Furthermore, as inter-arrival and execution times of interrupts are smaller than the granularity of the online dispatcher and the arrival times are unknown, interrupt-handling routines cannot be modeled as pre scheduled tasks. The application of server algorithms, e.g., sporadic server [Spr89] total bandwidth server [Spu94], and slack stealing [Leh92] are not feasible due to the short response times that are required.

The key issue for static scheduling accounting for interrupts is the consideration of the overhead. If interrupts occur at run-time, interrupt-handling routines are executed. The delay this poses on task execution must be accounted for when the system is scheduled. Evidently, an inherent, minimum amount - the worst case penalty - to handle a worst case scenario has to be reserved, according to minimum inter-arrival times and execution times. Any amount exceeding this, however, is overhead imposed by the used method. It is this overhead that has to be kept small for efficient utilization of the processor. During this project we had to develop a method that handled interrupts in an efficient manner. This method combines a tree search algorithm with response time analysis, see the paper by Sandström et al [San98].

**Finding 9**: To make a pre-run-time scheduler tool really useful, feedback has to be provided to the user when the system is not schedulable.

#### Motivation